# UNIVERSIDADE FEDERAL DO RIO GRANDE CENTRO DE CIÊNCIAS COMPUTACIONAIS PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO CURSO DE MESTRADO EM ENGENHARIA DE COMPUTAÇÃO

#### Dissertação

# Impacto da Radiação em Circuitos Sequenciais CMOS

Cristiano de Moura Borges

Dissertação apresentada ao Programa de Pós-Graduação em Computação da Universidade Federal do Rio Grande, como requisito parcial para a obtenção do grau de Mestre em Engenharia de Computação

Orientador: Prof. Dr. Paulo Francisco Butzen Coorientador: Prof. Dr. Rafael Budim Schvittz

#### B732i Borges, Cristiano de Moura

Impacto da radiação em circuitos sequenciais CMOS / Cristiano de Moura Borges. – 2025.

110 f.

Dissertação (Mestrado) – Universidade Federal do Rio Grande – Programa de Pós-Graduação em Computação, 2025.

Orientador: Dr. Paulo Francisco Butzen. Coorientador: Dr. Rafael Budim Schvittz.

1. Computação. 2. Radiação. 3. Semicondutores. 4. CMOS. I. Butzen, Paulo Francisco. II. Schvittz, Rafael Budim. III. Título.

**CDU 004**

#### Cristiano de Moura Borges

#### Impacto da Radiação em Circuitos Sequenciais CMOS

Dissertação apresentada ao Programa de Pós-Graduação em Computação da Universidade Federal do Rio Grande, como requisito parcial para a obtenção do grau de Mestre em Engenharia de Computação

Trabalho aprovado. Rio Grande, 28 de novembro de 2024:

Prof. Dr. Ewerson Luiz de Souza Carvalho

FURG - Universidade Federal de Rio Grande

Prof. Dr. Leomar Soares da Rosa Junior

UFPel - Universidade Federal de Pelotas Documento assinado digitalmente

PAULO FRANCISCO BUTZEN

Data: 25/09/2025 07:43:58-0300

Verifique em https://validar.iti.gov.br

Prof. Dr. Paulo Francisco Butzen (Orientador) UFRGS - Universidade Federal do Rio Grande do Sul

# Agradecimentos

Agradeço aos meus pacientes e dedicados orientadores pelas horas de conversa online além das horas de apoio ao desenvolvimento deste trabalho, agradeço também por me "proibirem de desistir". Agradeço a minha esposa e filha por todo o incentivo e amor e por serem a minha razão de tudo, além de serem sempre o motivo "de me faltarem palavras". Meus pais que a bem pouco se foram e que jamais deixaram de acreditar e confiar em mim e me dar os empurrões de que eu precisava. Aos meus "patrões" Edemir Eicholz e Rodrigo Borges da Rosa pelo tempo cedido para que pudesse comparecer às aulas e me dedicar ao trabalho, não da empresa, mas do mestrado, e aos colegas dos outros trabalhos, cito Faculdade Anhanguera de Rio Grande pelo incentivo e apoio e aos do IFSul também pelo incentivo e algumas vezes orientação.

### Resumo

A constante redução nas dimensões dos dispositivos integrados, possibilitou avanços no desempenho de computadores uma vez que a área é um recurso limitado. O uso das nano-tecnologias é a solução para atender a essa demanda. Entretanto, com a redução das escalas (scaling), com aumento da frequência de operação e com a redução da tensão de alimentação, surge uma maior suscetibilidade dos circuitos à colisão de partículas. Este trabalho tem como objetivo a investigação da interação das partículas de radiação com os circuitos sequenciais, que podem alterar o seu funcionamento ou suas características. A investigação se dará explorando o funcionamento dos dispositivos CMOS, entendendo a tecnologia e simulando eletricamente o resultado da ação da radiação nestes circuitos. Neste trabalho é apresentada uma revisão bibliográfica contendo a estrutura e funcionamento de transistores MOS, a tecnologia CMOS e seu uso na construção dos Flip-Flops, dispositivos indispensáveis à construção da atual tecnologia computacional. Após são explorados os dispositivos sequenciais Flip-Flops, construídos a partir de inversores e, por fim, executadas simulações elétricas de falhas transientes causadas pela radiação e alguns dos efeitos ocasionados pela radiação, como atrasos e perdas de dados. Considerando que o desempenho de sistemas computacionais é ligado ao desempenho de forma encadeada de diversos dispositivos, avaliar os efeitos da ação das partículas que podem afetar o funcionamento adequado dos componentes é extremamente importante, uma vez que o acúmulo de alterações nos diversos dispositivos de um sistema causariam falhas. As informações obtidas definem a quantidade de carga  $m coletada~(~Q_{coll})$  para desencadear uma mudança no estado do sinal de saída, gerando uma resposta dinâmica e dependente da magnitude e do tempo de existência do pulso de corrente. Tudo isto visualizado após a aplicação da dupla exponencial, modelo matemático utilizado para as simulações. Observa-se que não há uma Q<sub>crit</sub> constante, mas dependente das características do pulso de radiação e à resposta dinâmica do circuito, assim, um soft error será induzido quando um evento de radiação ocorre perto o suficiente de um nó sensível tal que  $Q_{coll} > Q_{crit}$ , ou seja, a carga coletada  $(Q_{coll})$  é maior que a carga crítica  $(Q_{crit})$ . Por outro lado, se o evento resultar em uma  $Q_{coll} < Q_{crit}$ , então não haverá ocorrência de  $soft\ error$ .

Palavras-chave: radiação, semicondutores, CMOS, carga crítica, soft error.

#### Abstract

The constant reduction in the dimensions of integrated devices has enabled advances in computer performance, since space is a limited resource. The use of nanotechnology is the solution to meet this demand. However, with the reduction in scale (scaling), with an increase in operating frequency and with a reduction in supply voltage, circuits become more susceptible to particle collisions. This work aims to investigate the interaction of radiation particles with sequential circuits, which can alter their operation or characteristics. The investigation will explore the operation of CMOS devices, understanding the technology and electrically simulating the result of the action of radiation on these circuits. This work presents a bibliographic review containing the structure and operation of MOS transistors, CMOS technology and its use in the construction of Flip-Flops, devices that are essential to the construction of current computer technology. After that, the Flip-Flops sequential devices, built from inverters, are explored and, finally, electrical simulations of transient faults caused by radiation and some of the effects caused by radiation, such as delays and data loss, are performed. Considering that the performance of computer systems is linked to the chained performance of several devices, evaluating the effects of the action of particles that can affect the proper functioning of the components is extremely important, since the accumulation of changes in the various devices of a system would cause failures. The information obtained defines the amount of charge collected  $(Q_{coll})$  to trigger a change in the state of the output signal, generating a dynamic response that depends on the magnitude and time of existence of the current pulse. All of this is visualized after applying the double exponential, a mathematical model used for the simulations. It is observed that there is no constant  $Q_{crit}$ , but rather it depends on the characteristics of the radiation pulse and the dynamic response of the circuit. Thus, a soft error will be induced when a radiation event occurs close enough to a sensitive node such that  $Q_{coll} > Q_{crit}$ —that is, the collected charge  $(Q_{coll})$  is greater than the critical charge  $(Q_{crit})$ . On the other hand, if the event results in a  $Q_{coll} < Q_{crit}$ , then there will be no *soft error* occurrence.

**Keywords**: radiation, semiconductors, CMOS, critical charge, soft error.

# Lista de ilustrações

| Figura 1 –  | Partículas, ondas, Radiação Natural e Artificial nas diversas ca-    |    |

|-------------|----------------------------------------------------------------------|----|

|             | madas da atmosfera e no solo terrestre. (Extraído de: (PRINZIE       |    |

|             | et al., 2021))                                                       | 19 |

| Figura 2 –  | Estruturas Cristalinas mostradas de forma plana. (a) Ligações        |    |

|             | covalentes no cristal de Si, (b) átomo de Arsênio (As) ligando-se ao |    |

|             | silício, formando o material n e (c) átomo de Boro (B) formando      |    |

|             | o material p. (Extraído de: (WESTE; HARRIS, 2015))                   | 24 |

| Figura 3 –  | Transistor pMOS de 4 terminais (Extraído de: (WESTE; HARRIS)         |    |

|             | 2015))                                                               | 26 |

| Figura 4 –  | Transistor da tecnologia CMOS. Ambos os transistores nMOS            |    |

|             | e pMOS em um único substrato. (Extraído de: (BOYLESTAD;              |    |

|             | NASHELSKY, 1984))                                                    | 27 |

| Figura 5 –  | Inversor CMOS. (Extraído de: (BOYLESTAD; NASHELSKY)                  |    |

|             | [1984])]                                                             | 28 |

| Figura 6 –  | Universalidade das portas NAND. (Adaptado de: (TOCCI; WID-           |    |

|             | MER; MOSS <mark>, 2010))</mark>                                      | 29 |

| Figura 7 –  | Porta NAND de duas entradas. (Adaptado de: (WESTE; HARRIS)           |    |

|             | 2015))                                                               | 30 |

| Figura 8 –  | Porta NOR de duas entradas. (Adaptado de: (WESTE; HARRIS,            |    |

|             | 2015))                                                               | 30 |

| Figura 9 –  | Rede pull-up/pull-down. (Adaptado de: (WESTE; HARRIS, 2015))         | 31 |

| Figura 10 - | Transistores de passagem e saídas forte e degradadas. (Adaptado      |    |

|             | de: (WESTE; HARRIS, 2015))                                           | 31 |

| Figura 11 - | - Porta de Transmissão (transmission gate). (Adaptado de: (WESTE;    |    |

|             | HARRIS <mark>, 2015))</mark>                                         | 32 |

| Figura 12 - | - Mecanismos de deposito de carga durante a interação iônica. (Ex-   |    |

|             | traído de: (WESTE; HARRIS, 2015))                                    | 36 |

| Figura 13 - | - Linha do tempo do pulso de corrente associado a colisão da partí-  |    |

|             | cula. (Extraído de: (WESTE; HARRIS, 2015))                           | 36 |

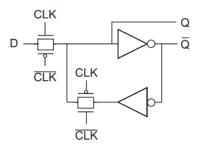

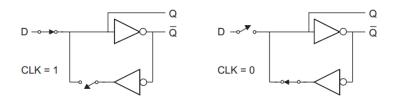

| Figura 14 - | - Latch D sensível ao nível alto do sinal de clock. Fonte: (WESTE;   |    |

|             | HARRIS <mark>, 2015)</mark>                                          | 40 |

| Figura 15 - | - Funiconamento do Latch D sensível ao nível alto do sinal de clock. |    |

|             | Fonte: (WESTE; HARRIS, 2015)                                         | 41 |

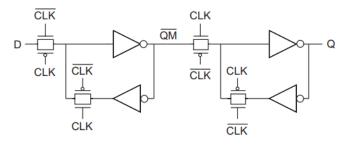

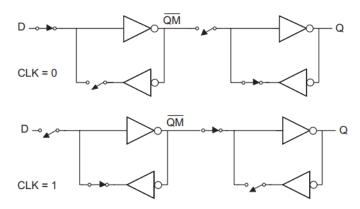

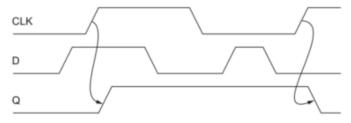

| Figura 16 - | - Flip-Flop D sensível à borda, Fonte: (WESTE: HARRIS 2015)          | 41 |

| Figura 17 - | - Funcionamento do Flip-Flop D sensível a borda. Fonte: (WESTE;                        |    |

|-------------|----------------------------------------------------------------------------------------|----|

|             | HARRIS <mark>,  </mark> 2015 <mark>)</mark>                                            | 41 |

| Figura 18 - | Formas de onda do FFDMS(+). Fonte: (WESTE; HARRIS, 2015)                               | 42 |

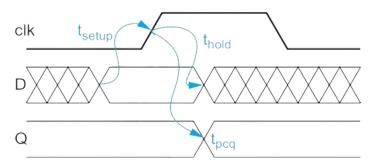

| Figura 19 - | Tempos de setup, hold e clock-to-Q. Fonte: (WESTE; HARRIS,                             |    |

|             | 2015)                                                                                  | 43 |

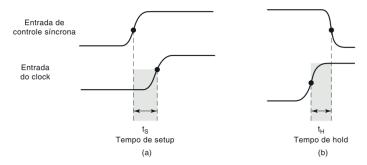

| Figura 20 - | Representação de t <sub>setup</sub> e t <sub>hold</sub> . Fonte: (TOCCI; WIDMER; MOSS, |    |

|             | 2010)                                                                                  | 44 |

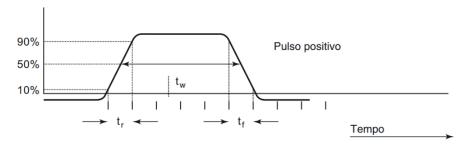

| Figura 21 - | Representação dos pontos de referência para medição de tempos e                        |    |

|             | pulsos. Fonte: (TOCCI; WIDMER; MOSS, 2010)                                             | 45 |

| Figura 22 - | - Resposta transitória para 5 MeV de partículas $\alpha$ no fenômeno de                |    |

|             | funneling. (Extraído de: (MESSENGER, 1982))                                            | 48 |

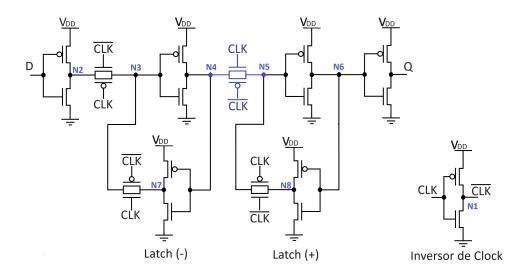

| Figura 23 - | - Esquemático do Flip-Flop D Mestre-Escravo. Fonte: O autor                            | 51 |

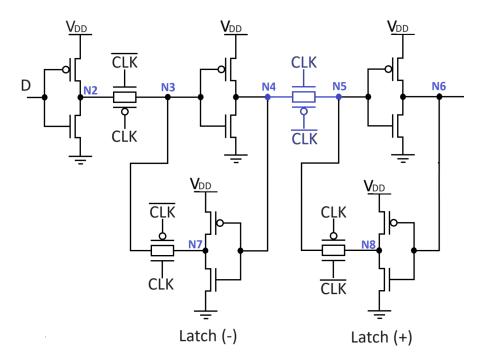

| Figura 24 - | - Esquemático do Flip-Flop D Mestre-escravo. Fonte: O autor                            | 52 |

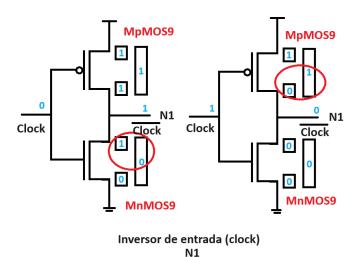

| Figura 25 - | - Diagrama criado pelo autor para ilustrar o efeito do sinal de en-                    |    |

|             | trada na sensibilidade à radiação de cada junção PN nos inversores                     |    |

|             | CMOS. Fonte: O autor                                                                   | 52 |

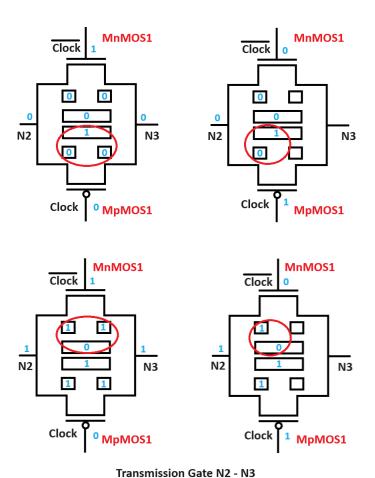

| Figura 26 - | - Ilustração criada pelo autor para indicar o efeito do sinal de entrada               |    |

|             | na sensibilidade à radiação de cada junção PN nas transmission                         |    |

|             | gates. Fonte: O autor                                                                  | 53 |

| Figura 27 - | - Validação lógica do Inversor. (Fonte: o autor)                                       | 57 |

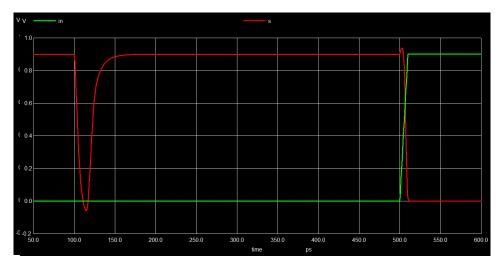

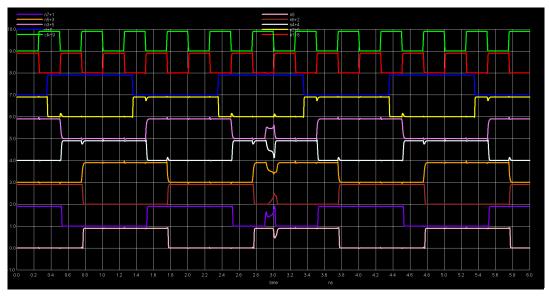

| Figura 28 - | - Resultado da simulação "101" para $I_2 = 90 \ \mu\text{A}$ , proveniente do          |    |

|             | campo elétrico provocado pelo SET. (Fonte: O autor)                                    | 59 |

| Figura 29 - | - Resultado da simulação "101" para $I_2 = 93~\mu\text{A}$ . (Fonte: O autor) .        | 59 |

| Figura 30 - | Resultado da simulação "101" para $I_2 = 96~\mu\text{A}$ . (Fonte: O autor) .          | 60 |

| Figura 31 - | - Resultado da simulação "010" para $I_2=127~\mu\mathrm{A}.$ (Fonte: O autor)          | 60 |

| Figura 32 - | Resultado da simulação "010" para $I_2=130~\mu\mathrm{A}.$ (Fonte: O autor)            | 61 |

| Figura 33 - | - Resultado da simulação "010" para $I_2=133~\mu\mathrm{A}.$ (Fonte: O autor)          | 61 |

| Figura 34 - | - Esquema do FFDMS. Fonte: (o autor)                                                   | 63 |

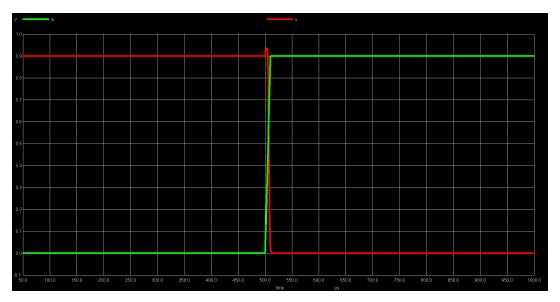

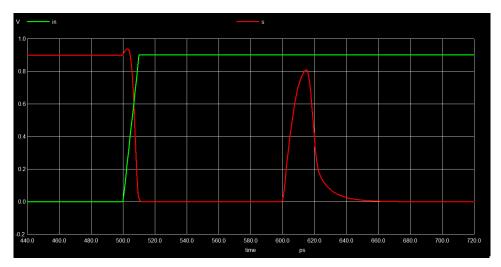

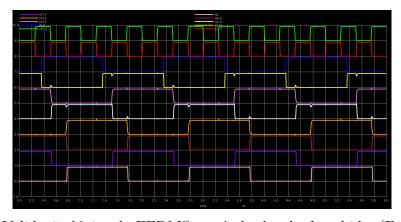

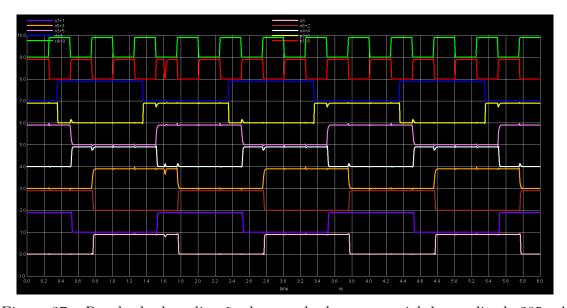

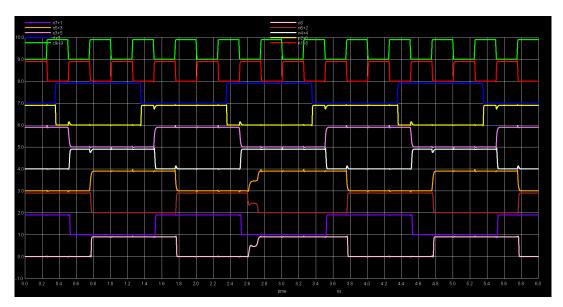

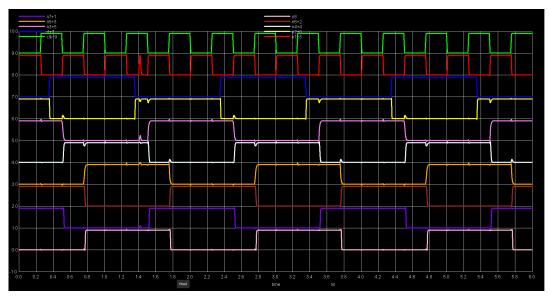

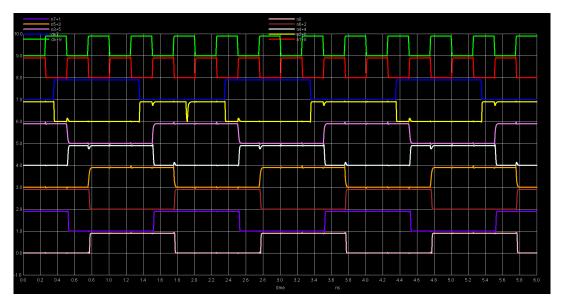

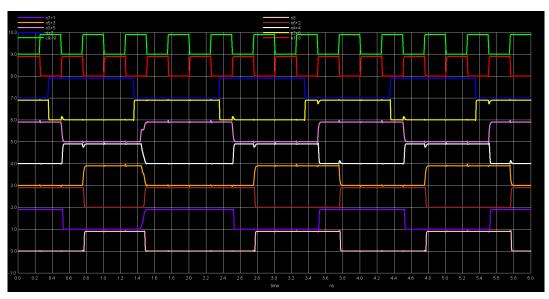

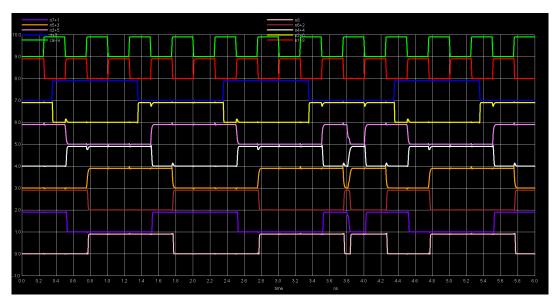

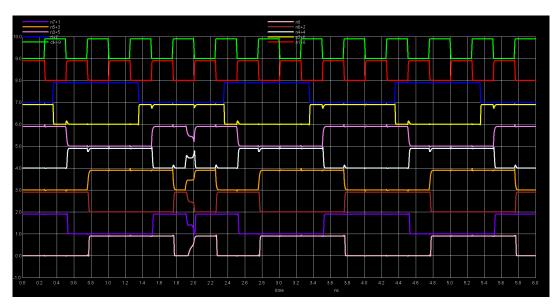

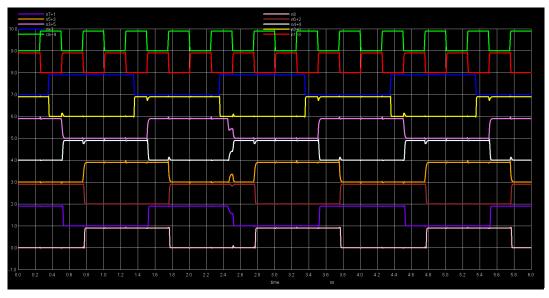

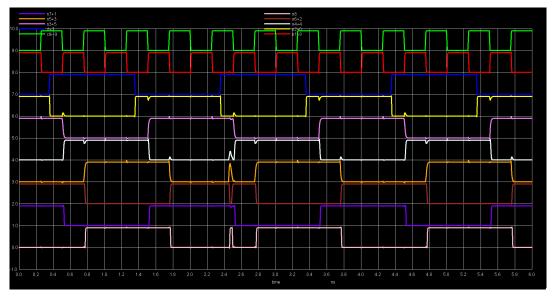

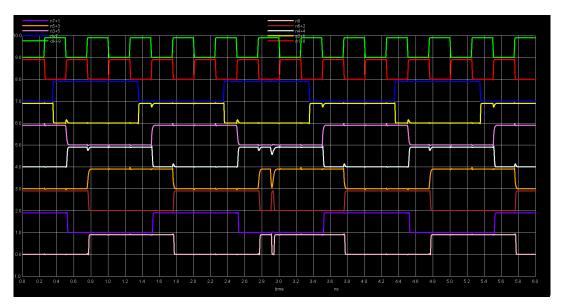

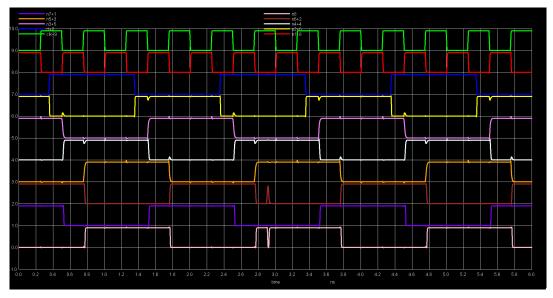

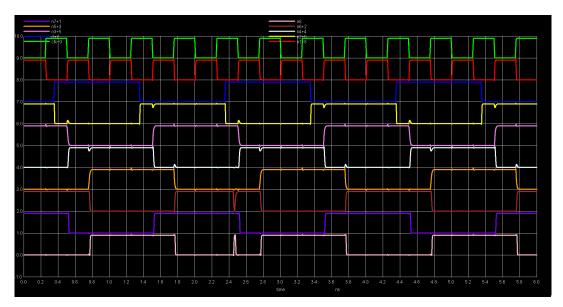

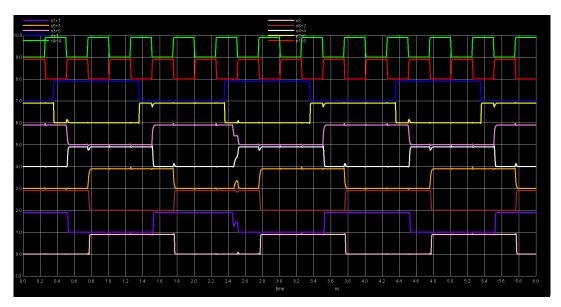

| Figura 35 - | - Validação lógica do FFDMS sensível a borda de subida. (Fonte: o                      |    |

|             | autor)                                                                                 | 65 |

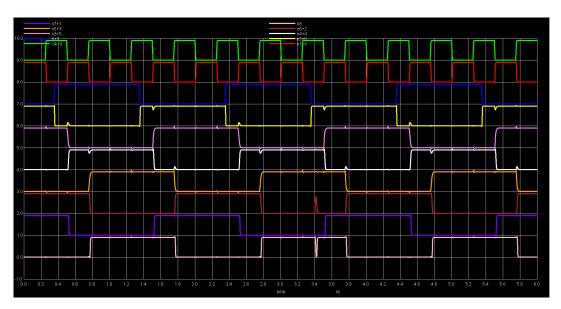

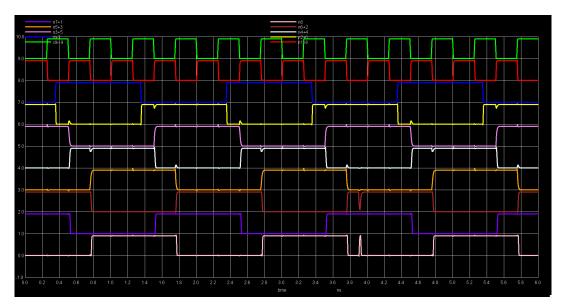

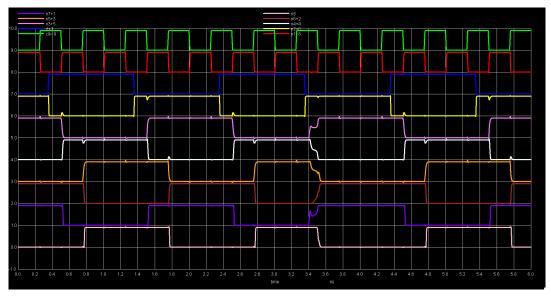

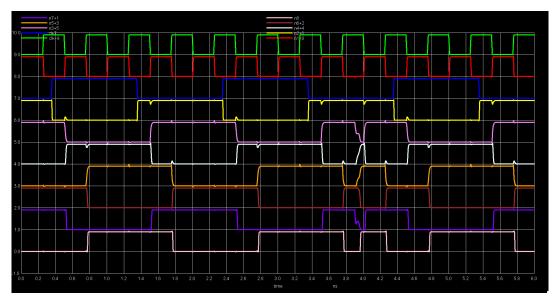

| Figura 36 - | - Identificação com cores das formas de onda. (Fonte: o autor)                         | 66 |

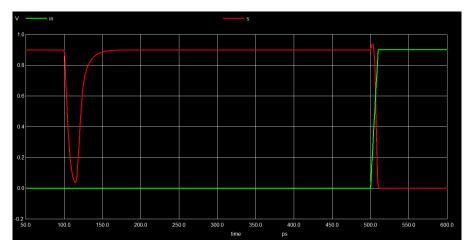

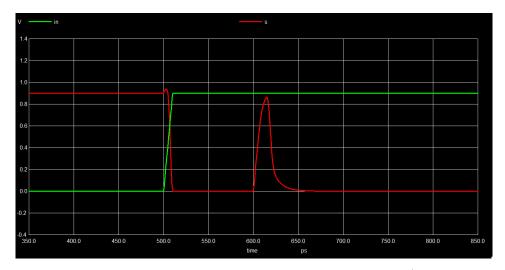

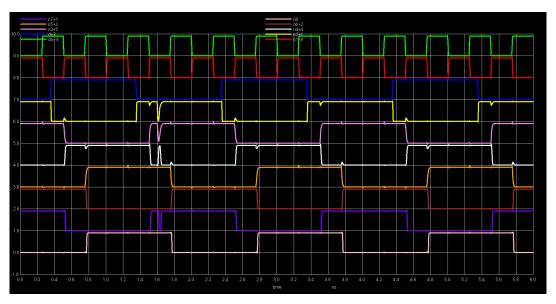

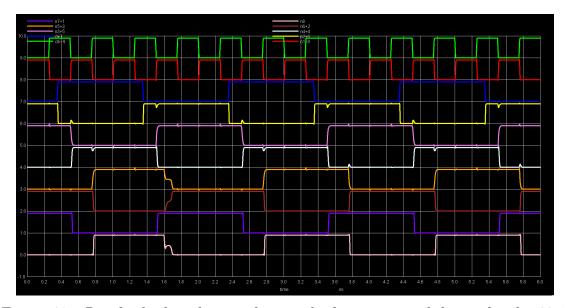

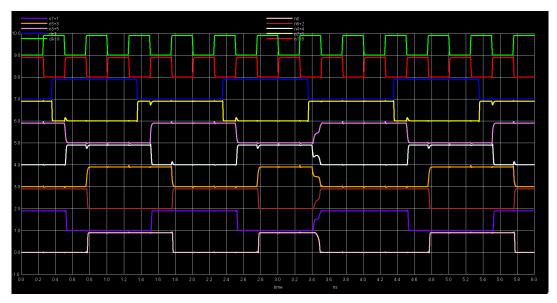

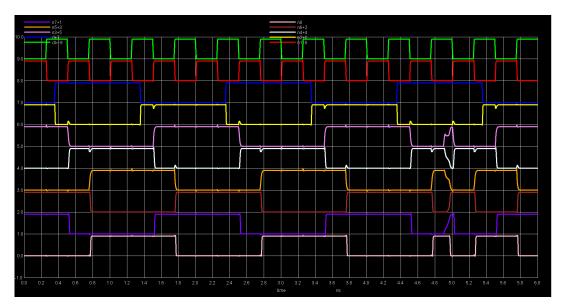

| Figura 37 - | - Resultado da aplicação de uma dupla exponencial de amplitude                         |    |

|             | $205~\mu\mathrm{A}$ ao nó N1 com vetor de entrada clock=0 e dados=0. (Fonte:           |    |

|             | o autor)                                                                               | 67 |

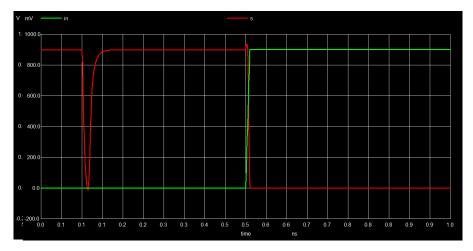

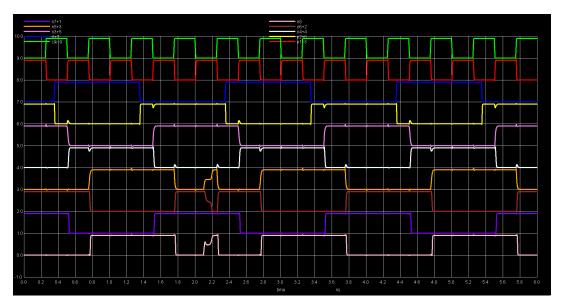

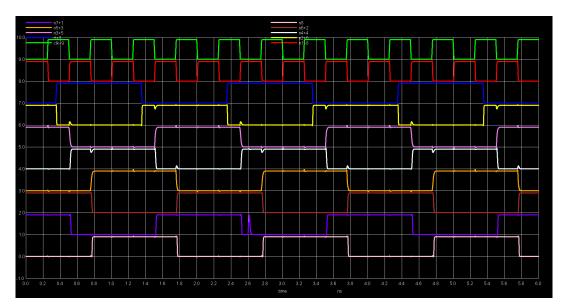

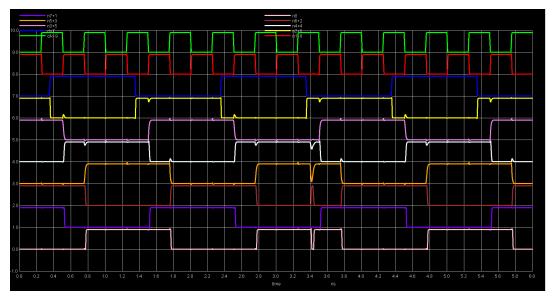

| Figura 38 - | - Resultado da aplicação de uma dupla exponencial de amplitude                         |    |

|             | $250~\mu\mathrm{A}$ ao nó N2 com vetor de entrada clock=0 e dados=0. (Fonte:           |    |

|             | o autor)                                                                               | 68 |

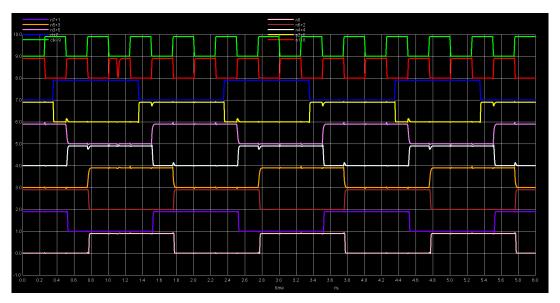

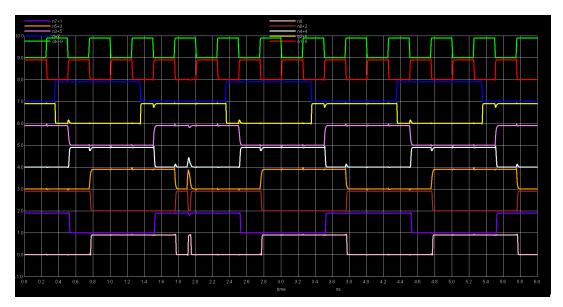

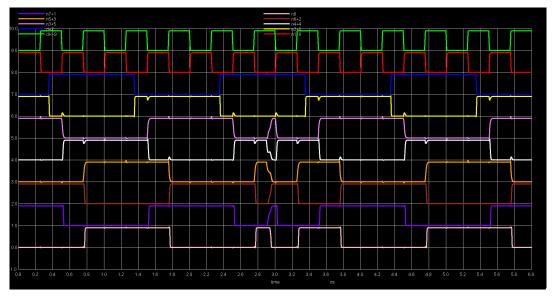

| Figura 39   | – Resultado da aplicação de uma dupla exponencial de amplitude               |          |

|-------------|------------------------------------------------------------------------------|----------|

|             | 150 $\mu$ A ao nó N3 com vetor de entrada clock=0 e dados=0. (Fonte:         |          |

|             | o autor)                                                                     | 68       |

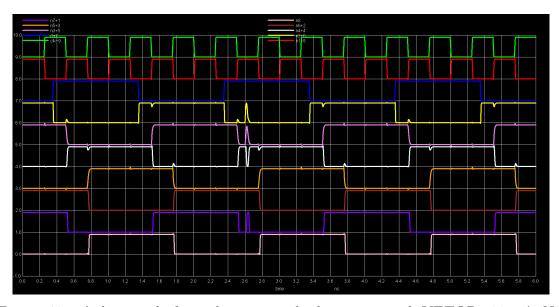

| Figura 40   | – Resultado da aplicação de uma dupla exponencial de amplitude               |          |

|             | $170~\mu\text{A}$ ao nó N4 com vetor de entrada clock=0 e dados=0. (Fonte:   |          |

|             | o autor)                                                                     | 69       |

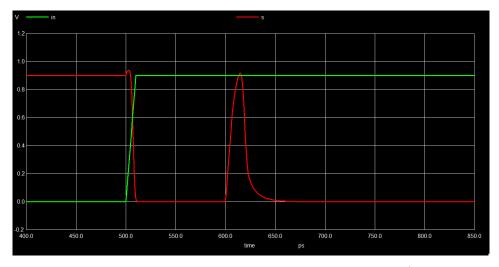

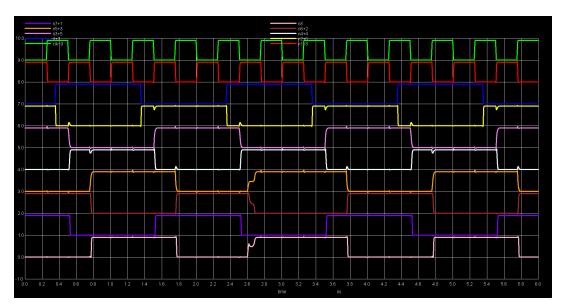

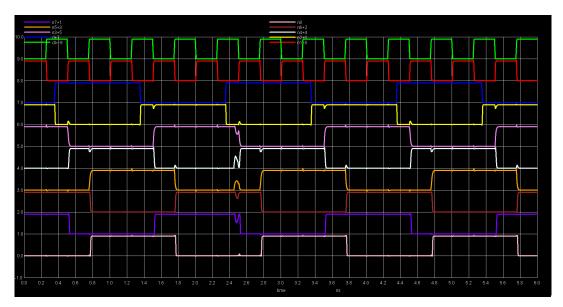

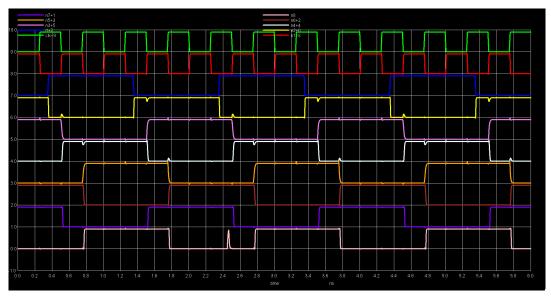

| Figura 41   | Resultado da aplicação de uma dupla exponencial de amplitude                 |          |

|             | 78,18 μA ao nó N5 com vetor de entrada clock=0 e dados=0.                    |          |

|             | (Fonte: o autor)                                                             | 70       |

| Figura 42   | Resultado da aplicação de uma dupla exponencial de amplitude                 |          |

|             | 79 $\mu$ A ao nó N4 com vetor de entrada clock=0 e dados=0. (Fonte:          |          |

|             | o autor)                                                                     | 71       |

| Figura 43   | – Resultado da aplicação de uma dupla exponencial de amplitude               |          |

|             | $124 \mu A$ ao nó N6 com vetor de entrada clock=0 e dados=0. (Fonte:         |          |

|             | o autor)                                                                     | 71       |

| Figura 44   | - Resultado da aplicação de uma dupla exponencial de amplitude               |          |

|             | 139,5 μA ao nó N6 com vetor de entrada clock=0 e dados=0.                    |          |

|             | (Fonte: o autor)                                                             | 72       |

| Figura 45   | – Resultado da aplicação de uma dupla exponencial de amplitude               |          |

|             | 198 $\mu$ A ao nó N7 com vetor de entrada clock=0 e dados=0. (Fonte:         |          |

|             | o autor)                                                                     | 73       |

| Figura 46   | - Resultado da aplicação de uma dupla exponencial de amplitude               |          |

|             | 177,5 μA ao nó N8 com vetor de entrada clock=0 e dados=0.                    |          |

|             | (Fonte: o autor)                                                             | 73       |

| Figura 47   | - Resultado da aplicação de uma dupla exponencial de amplitude               |          |

| 0           | $150.4 \mu A$ ao nó N8 com vetor de entrada clock=0 e dados=0.               |          |

|             | (Fonte: o autor)                                                             | 74       |

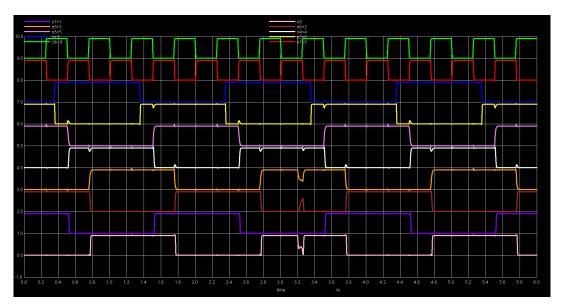

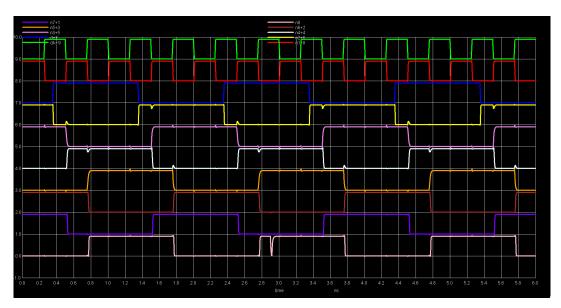

| Figura 48   | - Aplicação da fonte de corrente dupla exponencial: VETOR=01,                |          |

| 1 15uru 10  | $n\acute{o}=N1$ , corrente=206 $\mu A$ , tempo=1100ps, formato=nhit. (Fonte: |          |

|             | o autor)                                                                     | 75       |

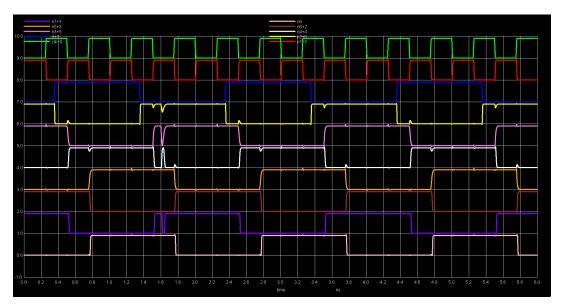

| Figura 49   | - Aplicação da fonte de corrente dupla exponencial: VETOR=01,                | 10       |

| rigura 45   | nó=N2, corrente=205 μA, tempo=2600ps, formato=phit. (Fonte:                  |          |

|             | o autor)                                                                     | 75       |

| Figura 50   | - Aplicação da fonte de corrente dupla exponencial: VETOR=01,                | 10       |

| rigura 50   |                                                                              |          |

|             | nó=N3, corrente=140 μA, tempo=2600ps, formato=phit. (Fonte:                  | 70       |

|             | o autor)                                                                     | 76       |

| Figura 51 - | • • •                                                                        | <b>—</b> |

|             | nó=N4, corrente=190 $\mu$ A, tempo=2600ps, formato=nhit                      | 76       |

| Figura 52 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=01,       |    |

|-------------|---------------------------------------------------------------------|----|

|             | nó=N5, corrente=78,7 $\mu$ A, tempo=2600ps, formato=phit. (Fonte:   |    |

|             | o autor)                                                            | 77 |

| Figura 53 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=01,       |    |

|             | nó=N5, corrente=80,1 $\mu$ A, tempo=3200ps, formato=nhit. (Fonte:   |    |

|             | o autor)                                                            | 77 |

| Figura 54 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=01,       |    |

|             | nó=N6, corrente=124,2 $\mu$ A, tempo=3200ps, formato=nhit. (Fonte:  |    |

|             | o autor)                                                            | 78 |

| Figura 55 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=01,       |    |

|             | nó=N6, corrente=139,39 $\mu$ A, tempo=2600ps, formato=nhit. (Fonte: |    |

|             | o autor)                                                            | 78 |

| Figura 56 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=01,       |    |

|             | nó=N7, corrente=148,5 $\mu$ A, tempo=2600ps, formato=phit. (Fonte:  |    |

|             | o autor)                                                            | 79 |

| Figura 57 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=01,       |    |

|             | nó=N8, corrente=150,5 $\mu$ A, tempo=2600ps, formato=phit. (Fonte:  |    |

|             | o autor)                                                            | 79 |

| Figura 58 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=01,       |    |

|             | nó=N8, corrente=177,8 $\mu$ A, tempo=3200ps, formato=nhit. (Fonte:  |    |

|             | o autor)                                                            | 80 |

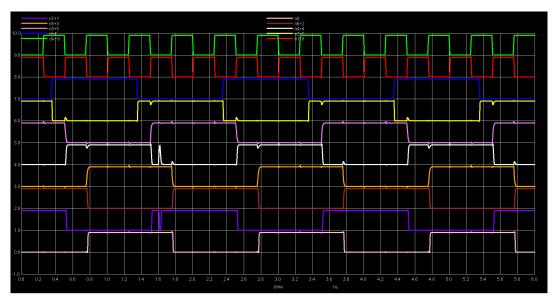

| Figura 59 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=10,       |    |

|             | nó=N1, corrente=156 $\mu$ A, tempo=1400ps, formato=phit. (Fonte:    |    |

|             | o autor)                                                            | 80 |

| Figura 60 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=10,       |    |

|             | nó=N2, corrente=195 $\mu$ A, tempo=3800ps, formato=nhit. (Fonte:    |    |

|             | o autor)                                                            | 81 |

| Figura 61 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=10,       |    |

|             | nó=N3, corrente=89 $\mu$ A, tempo=1430ps, formato=phit. (Fonte: o   |    |

|             | autor)                                                              | 81 |

| Figura 62 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=10,       |    |

|             | nó=N3, corrente=93 $\mu$ A, tempo=3800ps, formato=nhit. (Fonte: o   |    |

|             | autor)                                                              | 82 |

| Figura 63 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=10,       |    |

|             | nó=N4, corrente=152,85 $\mu$ A, tempo=1900ps, formato=phit. (Fonte: |    |

|             | o autor)                                                            | 82 |

| Figura 64 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=10,       |    |

|             | nó=N4, corrente=166,4 $\mu$ A, tempo=3400ps, formato=nhit. (Fonte:  |    |

|             | o autor)                                                            | 83 |

| Figura 65 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=10,       |    |

|-------------|---------------------------------------------------------------------|----|

|             | nó=N5, corrente=145 $\mu$ A, tempo=3400ps, formato=nhit. (Fonte:    |    |

|             | o autor)                                                            | 83 |

| Figura 66 - | – Aplicação da fonte de corrente dupla exponencial: VETOR=10,       |    |

|             | nó=N5, corrente=153 $\mu$ A, tempo=1900ps, formato=nhit. (Fonte:    |    |

|             | o autor)                                                            | 84 |

| Figura 67 - | – Aplicação da fonte de corrente dupla exponencial: VETOR=10,       |    |

|             | nó=N6, corrente=153 $\mu$ A, tempo=3400ps, formato=phit. (Fonte:    |    |

|             | o autor)                                                            | 84 |

| Figura 68 - | – Aplicação da fonte de corrente dupla exponencial: VETOR=10,       |    |

|             | nó=N6, corrente=200 $\mu$ A, tempo=3900ps, formato=nhit. (Fonte:    |    |

|             | o autor)                                                            | 85 |

| Figura 69 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=10,       |    |

|             | nó=N7, corrente=160,81 $\mu$ A, tempo=3400ps, formato=phit. (Fonte: |    |

|             | o autor)                                                            | 85 |

| Figura 70 - | – Aplicação da fonte de corrente dupla exponencial: VETOR=10,       |    |

|             | nó=N7, corrente=188 $\mu$ A, tempo=3900ps, formato=nhit. (Fonte:    |    |

|             | o autor)                                                            | 86 |

| Figura 71 - | – Aplicação da fonte de corrente dupla exponencial: VETOR=10,       |    |

|             | nó=N8, corrente=149 $\mu$ A, tempo=1900ps, formato=phit. (Fonte:    |    |

|             | o autor)                                                            | 86 |

| Figura 72 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=10,       |    |

|             | nó=N8, corrente=197 $\mu$ A, tempo=3400ps, formato=nhit. (Fonte:    |    |

|             | o autor)                                                            | 87 |

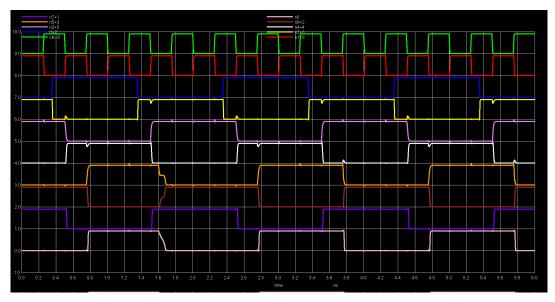

| Figura 73 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=11,       |    |

|             | nó=N1, corrente=160 $\mu$ A, tempo=2900ps, formato=phit. (Fonte:    |    |

|             | o autor)                                                            | 87 |

| Figura 74 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=11,       |    |

|             | nó=N2, corrente=140 $\mu$ A, tempo=2900ps, formato=phit. (Fonte:    |    |

|             | o autor)                                                            | 88 |

| Figura 75 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=11,       |    |

|             | nó=N3, corrente=86,55 $\mu$ A, tempo=2450ps, formato=nhit. (Fonte:  |    |

|             | o autor)                                                            | 88 |

| Figura 76 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=11,       |    |

|             | nó=N3, corrente=87,8 $\mu$ A, tempo=4900ps, formato=phit. (Fonte:   |    |

|             | o autor)                                                            | 89 |

| Figura 77   | – Aplicação da fonte de corrente dupla exponencial: VETOR=11,       |    |

|             | nó=N4, corrente=168 $\mu$ A, tempo=2900ps, formato=nhit. (Fonte:    |    |

|             | o autor)                                                            | 89 |

| Figura 78 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=11,       |     |

|-------------|---------------------------------------------------------------------|-----|

|             | nó=N4, corrente=150 $\mu$ A, tempo=2450ps, formato=phit. (Fonte:    |     |

|             | o autor)                                                            | 90  |

| Figura 79 - | – Aplicação da fonte de corrente dupla exponencial: VETOR=11,       |     |

|             | nó=N5, corrente=148 $\mu$ A, tempo=2450ps, formato=phit. (Fonte:    |     |

|             | o autor)                                                            | 90  |

| Figura 80 - | Aplicação da fonte de corrente dupla exponencial: VETOR=11,         |     |

|             | nó=N5, corrente=151 $\mu$ A, tempo=2900ps, formato=nhit. (Fonte:    |     |

|             | o autor)                                                            | 91  |

| Figura 81 - | – Aplicação da fonte de corrente dupla exponencial: VETOR=11,       |     |

|             | nó=N6, corrente=154 $\mu$ A, tempo=2900ps, formato=phit. (Fonte:    |     |

|             | o autor)                                                            | 91  |

| Figura 82 - | – Aplicação da fonte de corrente dupla exponencial: VETOR=11,       |     |

|             | nó=N6, corrente=210 $\mu$ A, tempo=2450ps, formato=nhit. (Fonte:    |     |

|             | o autor)                                                            | 92  |

| Figura 83 - | – Aplicação da fonte de corrente dupla exponencial: VETOR=11,       |     |

|             | nó=N7, corrente=160,81 $\mu$ A, tempo=2900ps, formato=phit. (Fonte: |     |

|             | o autor)                                                            | 92  |

| Figura 84 - | – Aplicação da fonte de corrente dupla exponencial: VETOR=11,       |     |

|             | nó=N7, corrente=187 $\mu$ A, tempo=2450ps, formato=nhit. (Fonte:    |     |

|             | o autor)                                                            | 93  |

| Figura 85 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=11,       |     |

|             | nó=N8, corrente=145 $\mu$ A, tempo=2450ps, formato=phit. (Fonte:    |     |

|             | o autor)                                                            | 93  |

| Figura 86 - | - Aplicação da fonte de corrente dupla exponencial: VETOR=11,       |     |

|             | nó=N8, corrente=197 $\mu$ A, tempo=2900ps, formato=nhit. (Fonte:    |     |

|             | o autor)                                                            | 94  |

| Figura 87 - | – Figura completa dos vetores (sinais aplicados e suas derivações), |     |

|             | nós e nodos sensíveis do Flip-Flop estudado.                        | .10 |

# Lista de abreviaturas e siglas

GHz  $Giga\ Hertz - 10^9 Hz$

CPU Central Processing Unit

CMOS Complementary Metal-Oxide Semiconductor

SET Single Event Transients

TMR Triple Modular Redundancy

ATMR Approximate Triple Modular Redundancy

MOS Metal Oxide Silicon

nMOS Metal Oxide Silicon tipo n

pMOS Metal Oxide Silicon tipo p

GND Conexão ao terra ou ponto comum

MOSFET Transistor de Efeito de Campo de Semicondutor de Óxido Metálico

FET Field Effect Transistor

NML Noise Margin Low

NMH Noise Margin High

SEEs Single Event Effects

SET Single Event Transient

SEU Single Event Upset

LET Linear Energy Transfer

$Q_{coll}$  Carga coletada

Q<sub>crit</sub> Carga crítica

SER Soft error rate

TID Total Ionizing Dose

SER Soft error rate

$LET_{th}$  Linear Energy Transfer Threshold

HP High Performance

$V_{\rm th}$  Threshold Voltage

ASU Arizona State University

VLSI Very-Large-Scale Integration

DICE dual interlocked cell

TMR Triple Modular Redundancy

# Sumário

| 1                   | INTRODUÇÃO                                       | 18 |

|---------------------|--------------------------------------------------|----|

| 1.1                 | Objetivos                                        | 20 |

| 1.1.1               | Objetivos Estratégicos                           | 21 |

| 1.1.2               | Objetivos Específicos                            | 21 |

| 1.2                 | Motivação                                        | 21 |

| 1.3                 | Organização do Documento                         | 23 |

| 2                   | FUNDAMENTAÇÃO TEÓRICA                            | 24 |

| 2.1                 | Tecnologia CMOS                                  | 24 |

| 2.1.1               | Transistor MOS                                   | 24 |

| 2.1.2               | O Inversor CMOS                                  | 27 |

| 2.1.3               | Portas Universais                                | 29 |

| 2.1.4               | Portas Compostas                                 | 30 |

| 2.1.5               | Transistores de Passagem e Portas de Transmissão | 31 |

| 2.2                 | Falhas Causadas por Radiação                     | 32 |

| 2.2.1               | Single Event Effect (SEE)                        | 34 |

| 2.2.2               | Single Event Upset (SEU)                         | 35 |

| 2.3                 | Latches e Flip-Flops                             | 39 |

| 2.3.1               | Diferenças entre Latches e Flip-Flops            | 39 |

| 2.3.2               | Flip-Flop Mestre-escravo                         | 39 |

| 2.3.3               | Latch D Sensível ao Nível Alto                   | 40 |

| 2.3.4               | Flip-Flop D Mestre-Escravo                       | 41 |

| 2.3.5               | Hold Time e Setup Time                           | 42 |

| 3                   | METODOLOGIA DO TRABALHO                          | 47 |

| 3.1                 | Modelo para Simulação Elétrica (NGSPICE)         | 47 |

| 3.1.1               | Modelo da Dupla Exponencial                      | 47 |

| 3.1.2               | Pontos de Sensibilidade à Radiação               |    |

| 4                   | RESULTADOS E DISCUSSÃO                           | 56 |

| 4.1                 | Validação do Inversor CMOS                       |    |

| <b>4.1</b> .1       | Análise 101                                      |    |

| 4.1.1               | Análise 010                                      | 60 |

| 4.1.∠<br><b>4.2</b> | Validação do Flip-Flop D Master-Slave            |    |

| 4.2.1               | Aplicação da dupla exponencial                   | 66 |

| · · · 스 · 土         | A DIRECTOR DE CAUDITE CAUDITEIRIE                | U  |

| 4.2.2 | Gráficos das Respostas à exposição do Flip-Flop às Duplas Exponenciais |

|-------|------------------------------------------------------------------------|

|       | nos demais vetores                                                     |

| 4.3   | Vetor 01 - clock= 0; dados=1                                           |

| 4.4   | Vetor 10 - clock= 1; dados=0                                           |

| 4.5   | Vetor 11 - clock=1; dados=1                                            |

| 5     | CONSIDERAÇÕES FINAIS                                                   |

|       | REFERÊNCIAS                                                            |

|       | APÊNDICE A – MODELO PREDITIVO DE ALTA PERFOR-                          |

|       | MANCE (HP) BULK CMOS 10                                                |

|       | APÊNDICE B – NETLIST SPICE DE UM FLIP-FLOP D 10                        |

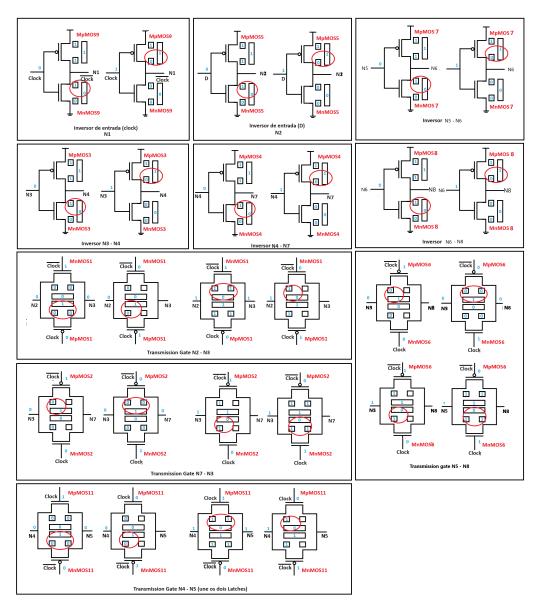

|       | APÊNDICE C – FIGURAS DOS INVERSORES E TRANS-                           |

|       | MISSION GATES CRIADAS PARA IDENTI-                                     |

|       | FICAR AS JUNÇÕES PN SENSÍVEIS SEN-                                     |

|       | SÍVEIS                                                                 |

## 1 Introdução

O avanço nos processos de integração empregados na fabricação de circuitos eletrônicos (VLSI) permitiu uma grande disseminação dos sistemas digitais facilitando que estes sejam utilizados nas mais diferentes aplicações na sociedade atual. Esta constante redução nas dimensões dos dispositivos integrados, possibilitou avanços no desempenho de computadores.

Uma vez que a área é um recurso limitado, o uso das tecnologias nanométricas é a solução para atender a essa demanda. Entretanto, com a redução do tamanho nas escalas de dimensionamento, no processo conhecido como *scaling*, acrescido do aumento da frequência de operação e da redução da tensão de alimentação dos circuitos, acabamos por permitir uma maior suscetibilidade dos circuitos à colisão de partículas (BAUMANN, 2005). Ao passo que esse mesmo avanço é responsável por tornar popular os sistemas embarcados, também tornou esses sistemas mais susceptíveis à falhas ocasionadas pela radiação, fazendo com que essas falhas passassem a ser cada vez mais consideradas durante o projeto dos sistemas digitais, fazendo com que o estudo das falhas esteja na atualidade presente como disciplina empregada na fase de projeto.

Os sistemas digitais atualmente operam em altas frequências (na faixa de vários GHz) e possuem, internamente, a nível de CPU (Unidade Central de Processamento), diversos circuitos sequenciais, capazes de armazenar e deslocar informações em formato binário. Estes circuitos são em sua grande maioria chamados de registradores. Eles são responsáveis por armazenar o estado em que o sistema computacional se encontra em dado momento. O bloco básico destes registradores, chamado de Flip-Flops, será o circuito foco da investigação apresentada nesta dissertação.

Atualmente grande parte da tecnologia direciona-se à pesquisa e desenvolvimento de dispositivos embarcados para sistemas autônomos como veículos terrestres, marítimos e aeronáuticos. Estes sistemas, além de precisão, demandam estabilidade em seus controles, economia de energia, redução de área,o que faz com que seja cada vez mais importante o desenvolvimento de técnicas que reforcem a capacidade de resiliência destes componentes à incidência de radiação, que tem na alta frequência de operação e na redução da tensão de alimentação, um caminho para o aumento da suscetibilidade dos circuitos em apresentar falhas decorrentes das interações com o meio. Essas interações ocorrem através de variações em fatores como: temperatura, umidade, vibração e também a qualquer tipo de radiação, objeto de estudo deste trabalho.

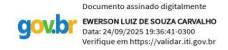

Figura 1 – Partículas, ondas, Radiação Natural e Artificial nas diversas camadas da atmosfera e no solo terrestre. (Extraído de: (PRINZIE et al., 2021))

Essa radiação pode ser originada de duas formas: (1) Eventos naturais, relacionados a partículas derivadas do espaço ou de materiais radioativos e (2), Eventos artificiais, relacionados à emissão eletromagnética originada de um equipamento eletrônico (AUTRAN; MUNTEANU), [2017]; (SAKURAI; MATSUZAWA; DOUSEKI, 2006) como os usadas em medicina, por exemplo. A figura 1 mostra diversos ambientes desde os mais inóspitos, como o espaço e em grandes altitudes ou ao nível do mar. Diante disso há diversos efeitos da radiação em dispositivos semicondutores. Esses efeitos podem variar em magnitude, causando desde interrupções no processamento e na transmissão de dados, até danos permanentes, que por sua vez, variam de mudanças paramétricas, ou seja, as funcionalidades dos dispositivos não mais são

alcançadas, o que faz com que as características mudem em definitivo, até a parada total do dispositivo.

A incidência de radiação faz com que haja a colisão de partículas, oriundas dos processos de emissão citados anteriormente, com os elétrons de partes sensíveis dos transistores responsáveis pela formação dos blocos lógicos sequenciais. Mesmo que os dispositivos não estejam em ambientes espaciais, fora da proteção oferecida pela atmosfera ou próximo de outros emissores de radiação como dispositivos de diagnóstico por imagem ou alguns sistemas industriais, passam a ocorrer alterações que afetam o comportamento dos circuitos integrados mesmo nos ambientes mais comuns, mesmo ao nível do mar.

Deve-se perceber que da mesma forma em que há progressos, vê-se também uma crescente de desafios. O padrão industrial CMOS após o atingimento dos 90 nm começou a apresentar problemas no aumento do consumo estático, aumento da variabilidade de processo, aumento dos efeitos de envelhecimento (agging) e uma série de efeitos negativos de segunda ordem no dispositivo. A solução foi utilizar novos materiais além do Silício ou Germânio, como as ligas híbridas de Silício e Germânio (GeSi) ou Arsenieto de Gálio (GaAs). Também substituiu-se o Dióxido de Silício (Si0<sub>2</sub>) por isolantes que possuem constante dielétrica maior (HUANG; YANG) CHU, 2010). No entanto, a cada novo nodo tecnológico os diferentes desafios de projeto tornavam mais difícil conciliar o crescimento do fator de integração, com as demandas exponenciais do mercado.

Algumas aplicações específicas exigem dos circuitos desenvolvidos, características especiais que não são prontamente atendidas utilizando-se as tecnologias e layouts convencionais. A radiação, com destaque para a do tipo ionizante, é capaz de danificar diretamente os circuitos integrados expostos, degradando progressivamente seu funcionamento. Podemos citar um ambiente crítico para circuitos eletrônicos que são os reatores de energia nuclear, onde diversos dispositivos responsáveis pelo controle do processo estão massivamente expostos a doses muito grandes de radiação. A solução do problema passa pela criação de estratégias que confiram resistência aos dispositivos eletrônicos expostos a essas condições, permitindo seu funcionamento confiável e preciso durante a vida útil prevista para o equipamento.

#### 1.1 Objetivos

Este trabalho tem como objetivo geral investigar as consequencias da interação das partículas de radiação que incindindo sobre uma junção PN, podem alterar o funcionamento ou até mesmo as características dos circuitos sequenciais, de forma mais específica, os Flip-Flops.

#### 1.1.1 Objetivos Estratégicos

- Conhecer o funcionamento dos transistores MOS (FET).

- Entender a tecnologia CMOS.

- Conhecer o funcionamento de circuitos sequenciais CMOS.

#### 1.1.2 Objetivos Específicos

- Revisar topologias de Flip-Flops tipo D e descrever o netlist de transistores de um Flip-Flop D Master/Slave.

- Simular eletricamente o resultado da ação não destrutiva da radiação nesses circuitos, visando oferecer embasamento para possíveis tomadas de atitudes para a redução de perdas por ação da radiação.

- Verificar as características da interferência em forma de pulso elétrico na inversão do valor de saída.

#### 1.2 Motivação

Considerando que o desempenho de sistemas computacionais, é ligado ao desempenho de forma encadeada de diversos dispositivos, avaliar os efeitos da ação da radiação em forma de partículas que podem afetar o funcionamento adequado dos componentes é extremamente importante, uma vez que o acúmulo de alterações, tanto nos circuitos combinacionais, quanto nos circuitos sequenciais, causariam falhas nos sistemas. Diversos trabalhos avaliam o impacto da radiação em células de memória SRAM [1-2] e muitos outros em lógica combinacional [3-4] mas poucos trabalhos fazem uma análise detalhada do impacto em blocos sequenciais como os Flip-Flops. Neste trabalho serão estudadas as falhas transientes devido a radiação, ou seja, SET (Single Event Transients) que acontecem quando uma partícula energizada colide com uma região sensível do transistor (GILL; SEIFERT; ZIA, 2009).

Essa partícula acaba por depositar carga nessa região, podendo alterar o estado do transistor causando a falha transiente que, dadas as proporções e grandezas envolvidas, podem provocar atrasos e alteração do valor lógico em uma entrada ou saída do componente.

Tomando como exemplo, a incidência de partículas em circuitos combinacionais, onde as falhas transientes afetam a saída atual do circuito. Enquanto isso em um circuito sequencial, o efeito transiente (SET) altera o valor armazenado até que uma nova operação de escrita ocorra no dispositivo. De maneira geral, um transistor em corte pode entrar em condução, modificando os valores armazenados ou de entrada e saída, e consequentemente, o comportamento do circuito.

No passado, esses efeitos transientes devido a radiação eram uma realidade apenas em ambientes espaciais, aeronáuticos e/ou caracterizado em ambientes hostis, expostos à índices de radiação gerada de forma artificial e que hoje são uma realidade até mesmo ao nível do mar (NICOLAIDIS, 2005).

Nesse contexto, uma das principais tendências é levar em consideração um SET como um parâmetro de projeto, mesmo em nível terrestre (MANABE et al., 2019), avaliando e adaptando os circuitos a níveis condizentes com a exposição, dada a tecnologia utilizada no mesmo.

Pensando como um efeito colateral da miniaturização (scaling) e da redução dos níveis de tensão aplicada nos circuitos, a sensibilidade aos efeitos de radiação, aumentou consideravelmente, tanto em relação ao estudo comportamental do efeito (BAUMANN, 2005), quanto no desenvolvimento e análise de uma variedade de modelos e técnicas de simulação e mitigação (SCHVITTZ et al., 2019) dessas falhas.

Para aumentar a confiabilidade de um sistema aos efeitos das falhas causadas por radiação, principalmente no caso de aplicações críticas, é comum a utilização de técnicas de endurecimento Radiation hardening by design - RHBD na etapa de projeto. Algumas das técnicas mais conhecidas e amplamente adotadas pelos projetistas para aumentar a robustez dos circuitos são as técnicas de Redundância Modular Tripla ou Triple Modular Redundancy (TMR) e a Redundância Modular Tripla Aproximada ou Approximate Triple Modular Redundancy (ATMR) de acordo com o visto em (OLIVEIRA, 2020), bem como a técnica Dual Interlocked Storage Cell (DICE) como poderão ser vistas no fichamento elaborado no estudo do estado da arte junto a diversas outras propostas inovadoras e algumas revisitadas.

Concluíndo, neste trabalho são apresentados a estrutura e funcionamento de transistores MOS e a implementação da tecnologia CMOS, os efeitos da radiação, o inversor CMOS, a aplicação da dupla exponencial na simulação da ação da radiação sobre os dispositivos em simulações no NGSpice, bem como os Flip-Flops, aplicando também a eles a dupla exponencial de Messenger para simulação de falhas transientes bem como estudo do estado da arte, buscando alternativas que aumentem a robustez destes dispositivos, reduzindo os efeitos de SET.

#### 1.3 Organização do Documento

Este trabalho está dividido da seguinte forma: o capítulo 2 que traz a Fundamentação Teórica onde são apresentados os conceitos preliminares que auxiliarão no entendimento do texto e das aplicações desenvolvidas durante o trabalho e reflete o estudo sobre o estado da arte. Prosseguindo, no capítulo 3 são apresentados os métodos de aquisição dos sinais, pontos de aplicação destes sinais no circuito proposto e suas respostas. Na sequência, o capítulo 4 apresenta os resultados obtidos e disserta sobre o procedimento narrado na metodologia, elencando os circuitos utilizados, sua validação lógica, e resultados preliminares, bem como o direcionamento para análise dos outros resultados em formas de onda elencados no Apêndice 4.2.2. Por fim, no capítulo 5 são evidenciadas as contribuições alcançadas até o momento.

## 2 Fundamentação Teórica

O objetivo desta seção é apresentar um panorama geral sobre os transistores MOS, visto em 2.1 e da tecnologia CMOS, trabalhada em 2.2. Para isso, ela trata dos seus principais componentes e topologias, do funcionamento do inversor CMOS no subitem 2.3, sua importância e funcionamento, das portas lógicas, sua universalidade e usos no item 2.4. Além disso, ela apresenta uma breve introdução à construção de portas lógicas compostas na topologia pull-up/pull-down, os transistores de passagem e as portas de transmissão no subitem 2.5, elementos indispensáveis para a elaboração dos Flip-Flops elencados no trabalho, base para o entendimento do estudo apresentado. É mostrado ainda o processo de falhas causadas pela incidência de radiação na seção 2.6.

#### 2.1 Tecnologia CMOS

Neste capítulo será revisado cada componente que forma a tecnologia CMOS, aplicada aos dispositivos foco de estudos deste volume, culminando com as falhas causadas por radiação a serem comprovadas através de simulações elétricas ao final do texto.

#### 2.1.1 Transistor MOS

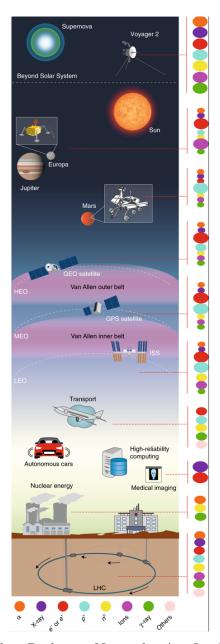

O silício (Si) é um semicondutor que forma o material inicial básico para a maioria dos circuitos integrados. O cristal de silício puro consiste em uma rede tridimensional de átomos e como o silício pertence ao Grupo IV da tabela periódica, forma ligações covalentes com quatro átomos adjacentes, conforme mostra a Figura [2].

Figura 2 – Estruturas Cristalinas mostradas de forma plana. (a) Ligações covalentes no cristal de Si, (b) átomo de Arsênio (As) ligando-se ao silício, formando o material n e (c) átomo de Boro (B) formando o material p. (Extraído de: (WESTE; HARRIS, 2015))

Uma vez que todos os seus elétrons de valência estão envolvidos em ligações químicas, o silício puro é um mau condutor de corrente e esta sua condutividade pode ser aumentada pela introdução de pequenas quantidades de dopantes, na rede cristalina de silício. Um dopante do Grupo V da tabela periódica, como o arsênio (As) tem cinco elétrons de valência, substituindo um átomo de silício da rede por um de arsênio, seu quinto elétron de valência ficará fracamente ligado ao átomo. A vibração térmica do cristal à temperatura ambiente é suficiente para deixar o elétron livre para se mover produzindo um íon As<sup>+</sup> carregado positivamente e um elétron livre. Havendo um número maior de elétrons livres é possível que haja corrente de elétrons, o que resulta em uma condutividade maior. Desta forma se origina um material semicondutor do tipo n por existir uma certa quantidade de portadores majoritários livres negativos (elétrons).

Da mesma forma, um dopante trivalente do Grupo III da tabela periódica, como por exemplo, o boro (B), que possuindo três elétrons de valência, pode ocupar ainda na ligação um elétron de um átomo de silício vizinho, o que por sua vez permite a formação de uma lacuna, ou seja, haverá a produção de um espaço que poderia ser ocupado por um outro elétron. Essa lacuna age como um portador positivo, por não conter um elétron, a profusão destas lacunas acaba dando origem a um semicondutor tipo p.

Uma estrutura de Semicondutor de Óxido Metálico (MOS) é criada pela sobreposição de várias camadas de materiais condutores e isolantes para formar uma estrutura tipo sanduíche (WESTE; HARRIS, 2015) utilizando o processo de fotolitografia. Essas estruturas são fabricadas usando uma série de processos físico-químicos que darão origem a um transistor que é um dispositivo de quatro terminais formado a partir de um substrato semicondutor dopado (tipicamente silício com fraca dopagem do tipo p), com uma concentração de dopantes de aproximadamente  $10^6$  a  $10^8$  átomos por cm<sup>3</sup>. A parte central da estrutura é coberta com uma fina camada de material isolante (normalmente dióxido de silício - SiO<sub>2</sub> ou simplesmente óxido fino) e sobre esta camada de óxido é então criado um eletrodo de baixa resistividade, chamado Porta (Gate) normalmente formado por silício policristalino altamente dopado (aproximadamente  $10^{20}$  átomos por cm<sup>3</sup>).

Quando há a junção de regiões dopadas com diferentes sinais (região do tipo P tem como portadores majoritários, as lacunas, enquanto uma região do tipo N tem como portadores majoritários, os elétrons) é formada uma região de depleção com menor concentração de portadores majoritários. Assume-se por simplificação, que esta região é bem definida, mas em verdade ela possui uma fronteira gradual dentro do semicondutor e é nesta região (região de depleção) que há a ocorrência das falhas transientes, quando esta região é trespassada por partículas.

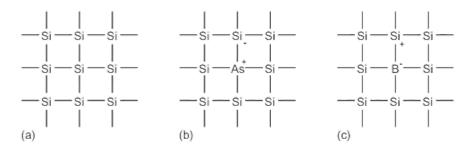

Para idealizar um transistor adiciona-se às laterais do dispositivo, através de implantação iônica, duas regiões fortemente dopadas de forma inversa ao substrato. Estas regiões são a princípio simétricas, chamadas de *Source* e *Drain* (Fonte e Dreno, respectivamente) conforme pode ser visto na figura [3].

Consideremos um transistor nMOS onde o substrato é geralmente aterrado de modo que as junções PN da fonte e do dreno para o corpo, região conhecida por substrato sejam polarizadas reversamente. Se a porta também estiver aterrada, nenhuma corrente fluirá pelas junções com polarização reversa. Portanto, dizemos que o transistor está em corte ou desligado, remetendo a uma chave que secciona o circuito. Se a tensão da porta aumenta, ela cria um campo elétrico que passa a atrair elétrons livres para a parte inferior da interface Si - SiO<sub>2</sub>. Havendo um aumento da tensão, o número de elétrons supera o de lacunas e uma região fina sob a porta chamada de canal é invertida para atuar como um semicondutor do tipo n. Portanto, um caminho condutor de elétrons é formado da fonte ao dreno e a corrente pode, assim fluir. Desta forma, diz-se que o transistor está LIGADO, permitindo que haja passagem de corrente elétrica.

Figura 3 – Transistor pMOS de 4 terminais (Extraído de: (WESTE; HARRIS, 2015))

Para um transistor pMOS, a situação é inversa. O substrato é mantido em uma tensão positiva. Quando a porta também está em uma tensão positiva, as junções de fonte e dreno são polarizadas reversamente e nenhuma corrente flui, deixando o transistor em estado de corte ou desligado. Quando a tensão da porta é reduzida, as cargas positivas são atraídas para a parte inferior da interface Si - SiO<sub>2</sub>. Uma tensão de porta suficientemente baixa inverte o canal e um caminho condutor de portadores positivos é formado da fonte ao dreno, de modo que o transistor será levado à condução.

Resumindo a ação do transitor MOS, sua porta controla o fluxo de corrente entre a fonte e o dreno. Simplificando ainda mais essa ação permitimos que os transistores MOS sejam vistos como interruptores liga/desliga. Quando a porta de um transistor nMOS estiver ligada à alimentação do circuito  $(V_{DD})$  seu nível lógico é considerado 1, o transistor estará ligado, pois existirá um caminho condutor da fonte para o dreno. Quando a porta está em nível baixo, ligada ao GND, o transistor

nMOS estará desligado e uma corrente próxima do zero flui da fonte para o dreno. Um transistor pMOS funcionará exatamente de forma oposta, sendo ligado quando a porta está em nível baixo e desligado quando a porta estiver em nível alto.

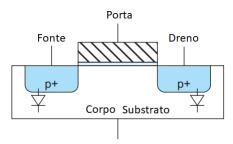

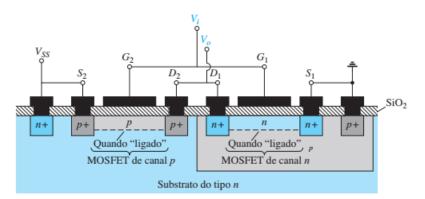

#### 2.1.2 O Inversor CMOS

A tecnologia CMOS utiliza os dois tipos de transistores: um transistor tipo n (nMOS) e um transistor tipo p (pMOS) em sua construção. As regiões n<sup>+</sup> e p<sup>+</sup> da Figura dindicam silício do tipo n ou p fortemente dopados, por elementos tri e pentavalentes. A operação do transistor é controlada por tensões geradas por campos elétricos, de modo que transistores MOS também são chamados de Transistores de Efeito de Campo de Semicondutor de Óxido Metálico (MOSFET) ou simplesmente Transistores de Efeito de Campo (FETs). É possível estabelecer um circuito lógico eficiente por meio da construção de um transistor usando um MOSFET de canal p e um de canal n no mesmo substrato. A configuração é chamada de arranjo MOSFET complementar ou CMOS (Complementary metal-oxide-semiconductor).

Figura 4 – Transistor da tecnologia CMOS. Ambos os transistores nMOS e pMOS em um único substrato. (Extraído de: (BOYLESTAD; NASHELSKY 1984))

A condição natural de um dispositivo CMOS de impedância de entrada alta, com uma também alta velocidade de chaveamento e os níveis reduzidos de potência de operação resultaram praticamente na elaboração de uma disciplina completamente nova, que pode ser chamada de Projeto por Lógica CMOS (BOYLESTAD; NASHELSKY, 1984). A partir dessa tecnologia, pode-se construir facilmente dispositivos lógicos ou associações desses dispositivos de forma a realizar algumas operações como por exemplo, inverter o valor de um sinal. Desta forma, a partir das ligações que podem ser observadas na figura 4 temos um inversor CMOS. (BOYLESTAD; NASHELSKY, 1984)

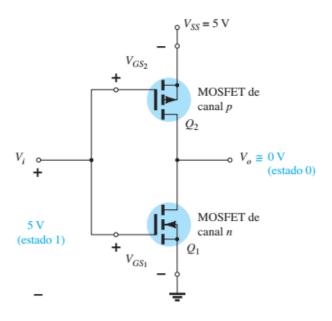

Analisando a Figura 5 percebe-se que ao aplicar uma tensão de 5 V (estado 1 ou nível alto) aos terminais das portas dos transistores nMOS e pMOS ( $V_i$ ) que

devem estar interligados e ambos os drenos à saída  $V_o$ . O terminal de fonte do MOSFET p  $(Q_2)$  está conectado diretamente à tensão aplicada  $V_{SS} = 5$  V, enquanto o terminal de fonte do MOSFET de canal n  $(Q_1)$  estará conectado ao terra. Para a aplicação de 5 V na entrada, devemos ter como resultado 0 V na saída (estado 0 ou nível baixo). Neste caso,  $V_{GS_1} = V_i$  e  $Q_1$  estará ligado, o que resulta em um valor baixo de resistência entre o dreno e a fonte. Visto que  $V_i$  e  $V_{SS}$  são iguais a 5 V,  $V_{GS_2} = 0$  V, resultando em um estado desligado, ou seja, o valor da resistência entre o dreno e a fonte é alto para  $Q_2$ . Nessas condições,  $V_o$  está em 0 V (estado 0 ou nível baixo) pela baixa resistência entre dreno e fonte do transistor  $Q_1$  o que o liga ao terra.

Figura 5 – Inversor CMOS. (Extraído de: (BOYLESTAD; NASHELSKY, 1984))

Quando aplicarmos nível baixo ao terminal conectado às portas dos transistores ( $V_i = 0$ ),  $V_{GS2} = V_i$  e  $Q_2$  estará ligado, o que resulta em um valor baixo de resistência entre o dreno e a fonte de  $Q_2$ , tornando a saída  $V_o = V_{SS}$ . Nos dois casos, podemos verificar a inversão dos valores de entrada ( $V_i$ ) com os valores de saída ( $V_o$ ). Como a corrente de dreno que flui em cada caso é limitada pelo transistor desligado a uma pequena corrente de fuga, a potência que o dispositivo dissipa em cada um dos dois estados é muito baixa (BOYLESTAD; NASHELSKY, 1984).

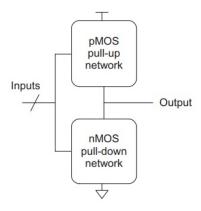

O inversor é um exemplo de porta lógica CMOS estática. Normalmente, uma porta CMOS estática apresenta uma rede *pull-down* nMOS para conectar a saída a 0 (GND) e uma rede *pull-up* pMOS para conectar a saída a 1 (V<sub>DD</sub>). As redes são organizadas de forma que uma esteja ligada e a outra desligada para qualquer padrão de entrada (WESTE; HARRIS, 2015).

As redes pull-up e pull-down no inversor consistem cada uma em um único

transistor, enquanto redes mais elaboradas são usadas para portas mais complexas. Usando combinações dessas construções temos a tecnologia CMOS combinacional com a qual diversas portas podem ser construídas (WESTE; HARRIS, 2015). Em contraste com outras formas de lógica, as portas CMOS estáticas operam corretamente, independentemente dos tamanhos físicos dos transistores.

Uma consequência do projeto de portas CMOS estáticas é que elas devem ser invertidas. A rede *pull-down* nMOS liga quando as entradas são 1, levando a 0, a saída. Para construir uma porta não inversora não basta inverter os sentidos dos transistores, pois tanto o transistor nMOS quanto o transistores pMOS, produzirão saídas degradadas, ou seja, que não atingem as faixas de valores cabíveis para os níveis lógicos. Em vez disso, podemos construir funções não inversoras a partir de múltiplos estágios de portas inversoras, dessa forma, cada projeto tem de ter diferentes compensações de velocidade, tamanho e potência.

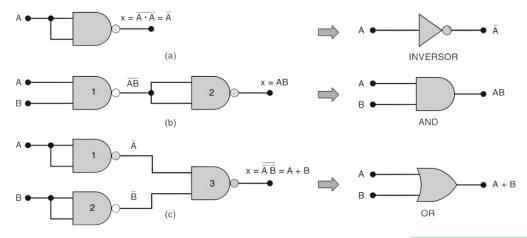

#### 2.1.3 Portas Universais

Assim como um inversor pode ser construído a partir de dois transistores MOS (nMOs e pMOS) podemos adotar conjuntos desses transistores para formar outras portas como as portas NAND e NOR. Estas portas de saída negada são universais e podem ser utilizadas em diversos tipos de circuitos. Todas as expressões booleanas consistem em combinações das operações básicas OR, AND e INVERSOR (TOCCI; WIDMER; MOSS, 2010) como pode ser visto na figura 6.

Figura 6 – Universalidade das portas NAND. (Adaptado de: (TOCCI; WIDMER: MOSS, 2010))

Portanto, qualquer expressão pode ser implementada usando combinações de portas OR, portas AND e INVERSORES. Entretanto, é possível implementar qualquer expressão usando-se apenas portas NAND, pois, em combinações apropriadas,

podem ser usadas para implementar cada uma das operações booleanas OR, AND e INVERSOR. Bastando então, aplicar os teoremas de DeMorgan e Boole.

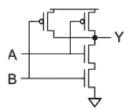

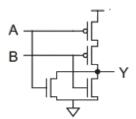

A Figura 7 mostra uma porta CMOS NAND de 2 entradas, que consiste em dois transistores nMOS série entre a saída Y e o GND e dois transistores pMOS paralelos entre a saída Y e o V<sub>DD</sub>. Se a entrada A ou B for 0, pelo menos um dos transistores nMOS estará DESLIGADO, ou seja, aberto, quebrando o caminho de Y à GND, mas pelo menos um dos transistores pMOS estará ligado, criando um caminho de Y à VDD. Portanto, a saída Y será 1. Se ambas as entradas forem 1, ambos os transistores nMOS estarão LIGADOS e ambos os transistores pMOS estarão DESLIGADOS. Assim, a saída será 0.

Figura 7 – Porta NAND de duas entradas. (Adaptado de: (WESTE; HARRIS, 2015))

Da mesma forma, uma porta NOR pode retornar resultado semelhante. Sua construção com a tecnologia CMOS é demonstrada na figura [8], onde os transistores nMOS estão em paralelo para retornar uma saída baixa quando uma das entradas é alta. Os transistores pMOS estão em série para retornar uma saída alta quando ambas as entradas são baixas.

Figura 8 – Porta NOR de duas entradas. (Adaptado de: (WESTE; HARRIS, 2015))

#### 2.1.4 Portas Compostas

Uma porta composta executa uma função lógica mais complexa em um único estágio de lógica e é formada pelo uso de uma combinação de estruturas de comutação em série e paralelo. Para tanto, os transistores que aparecem em série na rede pull-down devem aparecer em paralelo na rede pull-up e vice-versa.

Em geral, quando juntamos uma rede pull-up a uma rede pull-down para formar uma porta lógica como mostrado na figura [9], para cada vetor de entrada, somente um dos arranjos de transistores estará conduzindo a alimentação ou terra

para saída. Isso garante que a saída sempre tenha um valor lógico bem definido. É preciso lembrar que o resultado sempre se dará de forma invertida, necessitando que seja aplicado um inversor para se obter o resultado que se espera.

Figura 9 – Rede pull-up/pull-down. (Adaptado de: (WESTE; HARRIS, 2015))

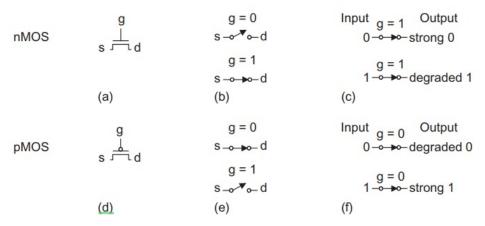

#### 2.1.5 Transistores de Passagem e Portas de Transmissão

A intensidade de um sinal é medida pelo quão próximo ele está de uma fonte de tensão ideal. Em geral, quanto mais forte for um sinal, mais corrente ele pode fornecer ou drenar. As fontes de alimentação, ( $V_{DD}$  e GND) são a fonte dos 1s e 0s. Um transistor nMOS é quase uma chave perfeita ao passar um 0 e, popularmente se diz que passa um 0 forte. No entanto, o transistor nMOS é imperfeito ao passar um 1. O nível de tensão é um pouco menor que  $V_{DD}$ , diz-se então, que passa um 1 degradado ou fraco. Um transistor pMOS tem o comportamento oposto. Os símbolos e comportamentos do transistor estão resumidos na figura  $\boxed{10}$  com g, s e d indicando porta, fonte e dreno, respectivamente.

Figura 10 – Transistores de passagem e saídas forte e degradadas. (Adaptado de: (WESTE; HARRIS, 2015))

Quando um transistor nMOS (ou um pMOS) é usado sozinho como uma chave imperfeita, o chamamos de transistor de passagem.

Combinando um transistor nMOS e um transistor pMOS em paralelo como podemos ver na Figura 11a, obtemos uma chave que liga quando 1 é aplicado a g e 0 é aplicado a gb (Figura 11b) na qual 0s e 1s são passados de maneira aceitável como pode ser visto na Figura 11c. A esta configuração chamamos de porta de transmissão ou porta de passagem. Em um circuito onde apenas 0 ou 1 precisa ser passado, o transistor apropriado (n ou p) pode ser excluído, revertendo para um único dispositivo nMOS ou pMOS. Alguns símbolos de circuito para a porta de transmissão são mostrado na Figura 11.

Input Output

$$g$$

$g = 0, gb = 1$   $g = 1, gb = 0$

$a \xrightarrow{\hspace{0.5cm}} b$   $g = 1, gb = 0$

$g =$

Figura 11 – Porta de Transmissão (transmission gate). (Adaptado de: (WESTE: HARRIS, 2015))

Os circuitos mostrados acima serão de grande importância na criação dos Flip-Flops a serem estudados neste trabalho, uma vez que estes são elaborados apenas com portas de transmissão (transmission gates) e inversores CMOS com transistores MOS na topologia pull-up/pull-down.

#### 2.2 Falhas Causadas por Radiação

Como mencionado anteriormente, à medida em que as dimensões e tensões de operação dos circuitos eletrônicos são reduzidas buscando satisfazer as demandas do mercado consumidor por maior densidade, funcionalidade e menor consumo energético, sua sensibilidade à radiação aumenta consideravelmente. A radiação pode afetar circuitos sequenciais, especialmente em ambientes de alta radiação como o espaço, em aplicações de controle em reatores nucleares ou áreas com radiação ionizante intensa. Esse fenômeno é muito preocupante para circuitos integrados e dispositivos eletrônicos avançados. A radiação afeta circuitos sequenciais provocando uma série de falhas e eventos, como:

Eventos Transitórios de Radiação (Single-Event Effects - SEE). Onde a radiação ionizante pode gerar pares elétron-lacunas em materiais semicondutores.

Isso provoca pulsos de corrente temporários nos transistores, que podem alterar os estados lógicos dos flip-flops e registradores em circuitos sequenciais.

Falhas de Soft (Soft Errors): Partículas de radiação podem mudar o valor armazenado em um elemento de memória (bit flip). No caso de circuitos sequenciais, isso afeta os estados armazenados no sistema, como os dados em um flip-flop ou registrador.

Degradação de Componentes (TID - Total Ionizing Dose): Ao longo do tempo, a exposição prolongada à radiação pode degradar os transistores MOSFETs. Isso altera tensões de limiar (Vt), impactando a operação estável de circuitos sequenciais através da interação entre partícula e material na qual a radiação ionizante (como partículas alfa, prótons ou nêutrons) interage com o silício, o material base dos circuitos integrados, gerando cargas indesejadas e maior sensibilidade de estados sequenciais. Dessa forma, torna-os mais sensíveis do que circuitos combinacionais pois estes armazenam estados, ou seja, uma alteração causada pela radiação pode persistir e comprometer a funcionalidade do circuito (SCHRIMPF; FLEETWOOD, 2004).

Vários efeitos de radiação podem ser observados nos semicondutores e estes efeitos podem variar em sua magnitude, proporcionando desde interrupções na transferência de dados, perda dos dados acumulados (DODD; MASSENGILL, 2003) até danos permanentes. Esses possíveis danos podem variar em índices que vão de mudanças paramétricas, onde os dispositivos perdem a capacidade de retomar seu funcionamento normal, uma vez que sofre alterações das suas características físicas e à falha permanente e destrutiva do dispositivo . Esses efeitos incluem: Bloqueio por single event (evento único), Burnout (queima) por single event, Gate Rupture por single event, e outros (SEXTON, 2003).

No presente trabalho, o foco serão os efeitos não permanentes, ou seja, aqueles efeitos transitórios que alteram os dados armazenados nos dispositivos, mas não alteram suas características físicas ou condição de funcionamento, uma vez que os danos se acumulam além do nível de tolerância do dispositivo, ele normalmente não pode ser recuperado.

De certa forma, a radiação pode ser interpretada como uma forma de energia em movimento que se propaga pelo meio através de partículas subatômicas de matéria (FRIEDBERG; COPELAND, 2011) através de um meio ou no vácuo, com origem natural ou artificial. Como exemplo de radiação de origem natural podem ser citadas as radiações cósmicas e dos ventos solares originadas no espaço e a radiação de solo radioativo originada no próprio planeta dadas as características radioativas pela presença de materiais radioativos de um determinado solo.

A radiação natural depende de qualquer fonte que não exija interferência externa para que haja emissão de partículas ou ondas eletromagnéticas. Enquanto isso, a radiação artificial surge como produto de processos atômicos ou nucleares, que ocorrem em máquinas e equipamentos, como por exemplo, em procedimentos médicos de radiografia, em aceleradores de partículas, em explosões de dispositivos nucleares e, inclusive, em tubos de raios catódicos utilizados em aparelhos de televisão e monitores de computadores (KNOLL, 2010). Portanto, mesmo que se imagine um circuito imune a radiações naturais ao nível do mar, outras influências artificiais podem levar a erros conhecidos como efeitos de eventos singulares, ou Single Event Effects (SEEs).

Falhas são causadas quando partículas subatômicas altamente carregadas energeticamente (elétrons, prótons, nêutrons, partículas alfa, píons, múons ou íons) atingem partes sensíveis de um circuito (DODD; MASSENGILL, 2003). Dependendo de vários fatores, o impacto dessas partículas pode causar desde nenhum efeito observável, passando pela interrupção transitória de uma operação, por uma mudança no estado lógico ou até mesmo por um dano permanente e irreversível ao circuito integrado.

Quando a radiação faz contato com um átomo, seja através de uma partícula ou de uma onda eletromagnética, a energia liberada pela colisão entre essas partículas pode afetar sua estrutura atômica. Se a energia liberada pela colisão superar a energia de ligação entre as partículas do átomo, ocorrerá uma ionização ou reação nuclear. Caso a energia seja inferior a energia de ligação, causará um deslocamento entre as partículas causando fenômenos que podem ser denominados de radiação ionizante e não ionizante respectivamente.

Considerando apenas a radiação ionizante, teremos como principais fontes, os elementos radioativos ou os raios cósmicos que consistem em partículas de alta intensidade, produzidas por diversos corpos cósmicos e são considerados partículas primárias que colidem com os átomos na atmosfera, liberando novas partículas subatômicas secundárias altamente ionizadas (FRIEDBERG; COPELAND, 2011). Assim eles dão origem a um efeito em cadeia (radiação ionizante) onde os efeitos proporcionam o surgimento de novas partículas, além da liberação de mais radiação durante o processo. Por outro lado, na radiação não ionizante os efeitos geralmente se resumem a agitação das moléculas e geração de calor.

#### 2.2.1 Single Event Effect (SEE)

As falhas transientes de efeito único devido à radiação acontecem quando uma partícula colide com uma região sensível do transistor gerando um Single Event Effect

(SEE) quando essa partícula acaba depositando carga nessa região, podendo alterar o estado do transistor (BAUMANN, 2005). A falha ocorre quando um valor lógico é alterado em decorrência da interação com o ambiente externo e tem efeito de curto prazo sobre o componente ou circuito que acaba por retornar à normalidade. Usando como exemplo, um circuito combinacional, as falhas afetam a saída do circuito e em circuitos sequenciais, o efeito transiente altera o valor armazenado até que uma nova operação de escrita ocorra no dispositivo.

Os efeitos transientes são uma realidade até mesmo ao nível do mar e em ambientes do nosso dia-a-dia devido à miniaturização dos circuitos e à menor aplicação de energia na sua alimentação. Desta forma, a comunidade de projetistas tem como uma das principais tendências atualmente, considerar *Soft Errors* como um parâmetro de projeto, mesmo em nível terrestre. Nesse contexto, os SEEs não destrutivos ou falhas transientes são reconhecidos como uma grande ameaça ao funcionamento dos dispositivos eletrônicos.

#### 2.2.2 Single Event Upset (SEU)

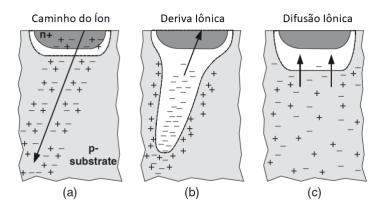

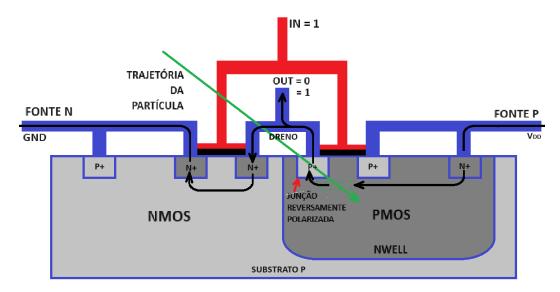

Em circuitos sequenciais, um dos principais efeitos de radiação é denominado como Single Event Upset (SEU) que ocorre quando uma partícula ionizada colide com a junção PN de um transistor reversamente polarizado, colisão esta que "deposita" pares de elétrons-lacunas, que serão coletados como carga pelo dispositivo através de dois mecanismos: Drift (Deriva) e Diffusion (Difusão).

O mecanismo de *Drift* ocorre quando a partícula percorre a região de depleção onde um campo elétrico gerado por ela coleta os portadores excedentes o que implica em uma deformação temporária da região de depleção, denominada *Funneling*, ou seja, um afunilamento da região (BAUMANN, 2005). Já o mecanismo de *Diffusion* ou difusão, é responsável por coletar os portadores gerados fora da região de depleção. Se a carga acumulada durante esses processos for maior que a carga crítica suportada pelo dispositivo, este apresentará um desvio de comportamento. A Figura 12 ilustra os mecanismos de depósito de carga durante a interação iônica.

Na figura 12 é possível perceber a geração dos pares de elétron-lacunas em uma junção p-n reversamente polarizada: Em (a), ocorre a ionização do substrato no local da colisão da partícula e o caminho percorrido por ela; em (b) é mostrada a formação do funneling na região de depleção e em (c) a carga coletada na deriva é sobreposta pela carga coletada pela difusão.

Figura 12 – Mecanismos de deposito de carga durante a interação iônica. (Extraído de: (WESTE; HARRIS, 2015))

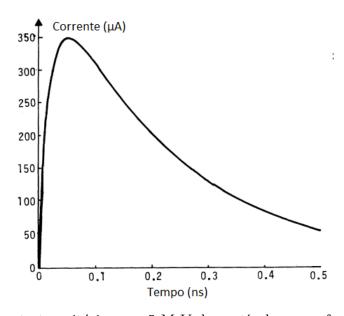

Para as simulações, à espelho de como foi utilizado em (MESSENGER, 1982), foi usado um modelo analítico que simula os efeitos da colisão da partícula através da inserção de uma fonte de corrente no sistema com uma forma de onda no formato de pulso, que obedece idealmente ao comportamento de uma dupla exponencial conforme a onda demonstrada na Figura [13], onde o evento inicia-se com a chegada da carga à junção PN, ionizando o substrato e gerando pares de portadores pelo caminho percorrido por ela. No espaço de tempo entre o ponto de coleta da carga e o momento onde inicia-se a difusão da carga coletada, situa-se o pico de corrente representado pela equação [2.1].

Figura 13 – Linha do tempo do pulso de corrente associado a colisão da partícula. (Extraído de: (WESTE; HARRIS, 2015))

Com base nesse modelo temos as equações 2.1 e 2.2,

$$I(t) = \left(\frac{Q_{\text{coll}}}{\tau \alpha - \tau \beta}\right) \times \left(e^{\frac{-t}{\tau \alpha}} - e^{\frac{-t}{\tau \beta}}\right) \tag{2.1}$$

$$Q_{\text{coll}} = 10.8 \times 10^{-15} (L)(LET) \tag{2.2}$$

onde:

- $\bullet$   $Q_{coll}$  é a quantidade de carga coletada;

- $\tau \alpha$  é a constante de tempo de carga;

- $\tau\beta$  é a constante de tempo para a formação da trilha do íon.

- $\bullet\,$  10,8 fC é a quantidade de carga depositada por micrômetro.

- $\bullet$  LET  $Linear\ Energy\ Transfer$  é a quantidade de energia por unidade de comprimento.

- L representa a profundidade do deposito de carga (caminho da deriva).

Todos os parâmetros envolvidos nas equações 2.1 e 2.2 servirão para que se possa contabilizar a quantidade de carga coletada durante a interação da partícula com as partes sensíveis do semicondutor e com isso obter o quanto esta carga coletada se aproxima do valor da carga crítica, o que nos daria a noção mais precisa de quanto se estaria próximo de uma alteração no nível do sinal original para alto ou baixo, provocando um SEU.

Devemos citar ainda, que o ambiente terrestre é dominado por mecanismos que geram (diretamente ou como produtos de reação secundária) íons que são responsáveis por induzir soft errors. A magnitude de uma perturbação depende da transferência linear de energia (LET, do inglês Linear Energy Transfer) desse íon que normalmente relatamos em unidades de MeV.cm²/mg (BAUMANN, 2005). O LET refere-se a quantidade de energia liberada por uma partícula por unidade de comprimento do caminho que essa partícula percorreu no semicondutor (WANG; AGRAWAL, 2008).

Conforme se vê na Figura  $\boxed{12}$ , no início de um evento de radiação ionizante, uma trilha cilíndrica, portanto, tridimensional de pares de elétrons lacunas com raio abaixo de 1  $\mu$ m e uma concentração muito alta de portadores é formada no caminho da passagem do íon energético em (a). Quando a trilha resultante da ionização atravessa ou se aproxima da região de depleção, portadores são rapidamente coletados pelo campo elétrico criando um grande transiente de corrente/tensão naquele nó.

Uma característica notável do evento é a distorção em forma de funil (funneling) durante a deriva iônica (HSIEH; MURLEY; O'BRIEN, 1981). Este funil aumenta muito a eficiência da coleta de deriva, estendendo a camada de depleção, o que é ilustrado em (b) e consequentemente, aumenta o tamanho do funil o que se dá em função da dopagem do substrato. Com esta fase da coleta concluída, após cerca de um nanossegundo, a difusão começa a dominar o processo de coleta de carga,

como visto em (c) ou seja, ascargas coletaddas começam a retornar aos seus lugares, recombinando-se.

A carga adicional é coletada à medida que os elétrons se difundem na região de depleção em uma escala de tempo mais longa (na casa de centenas de nanossegundos) até que todos os portadores em excesso tenham sido coletados, recombinados ou difundidos para longe da área de junção.

O pulso de corrente correspondente, resultante dessas três fases é mostrado na Figura [13] Em geral, quanto mais longe da junção o evento ocorrer, menor será a quantidade de carga coletada e dessa forma, menos provável que o evento cause um soft error.

Em circuitos reais, um nó nunca é isolado, na verdade é parte de um complexo de nós muito próximos uns dos outros; assim, compartilhamento de carga entre nós pode influenciar muito a quantidade de carga coletada  $(Q_{coll})$  e o valor e localização da tensão e da corrente de falhas no circuito.

De acordo com ( $\overline{BAUMANN}$ ,  $\overline{2005}$ ) a magnitude de  $Q_{coll}$  depende de uma combinação complexa de fatores, que incluem:

- o tamanho do dispositivo,

- a polarização dos vários nós do circuito,

- a estrutura do substrato,

- a dopagem do dispositivo,

- o tipo de íon,

- a sua energia,

- a sua trajetória,

- a posição inicial do evento dentro do dispositivo e o

- estado do dispositivo

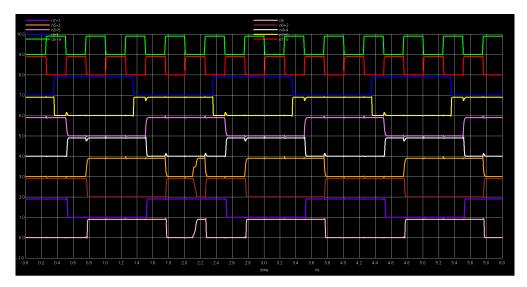

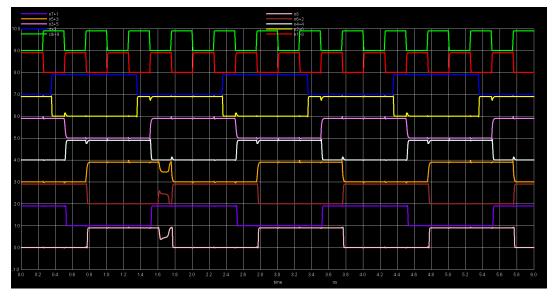

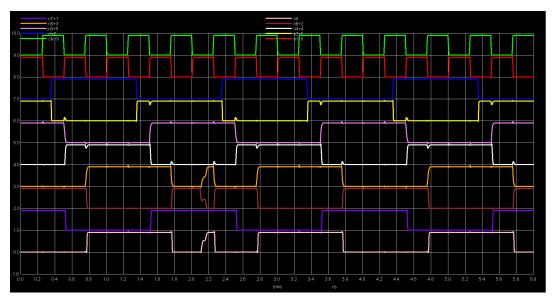

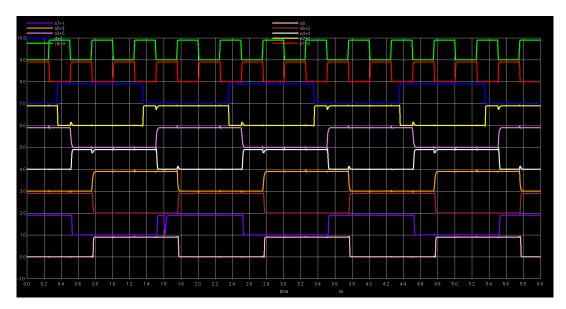

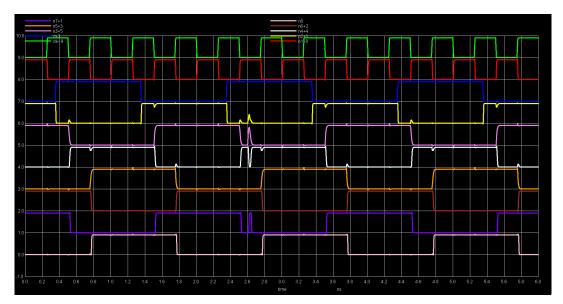

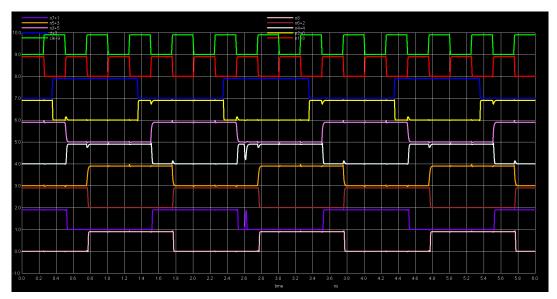

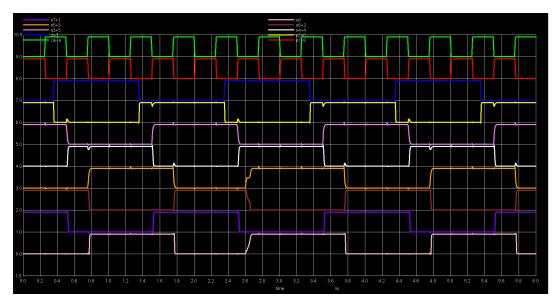

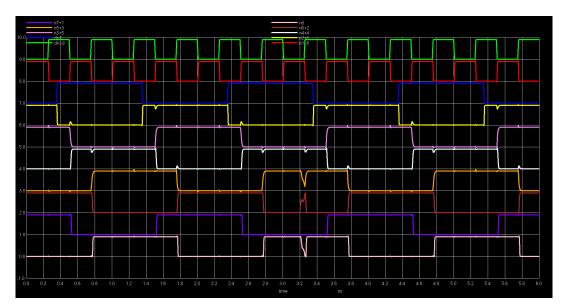

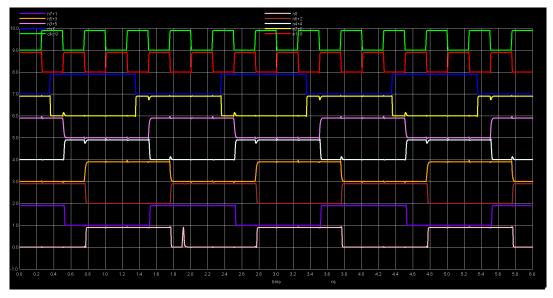

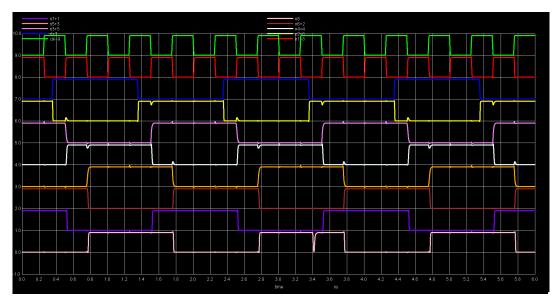

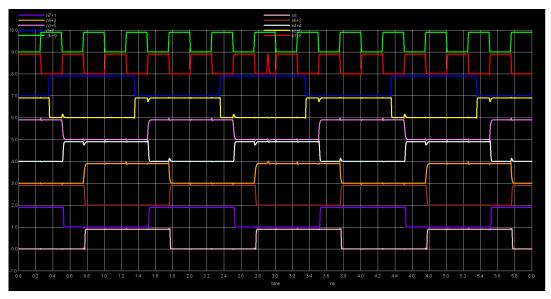

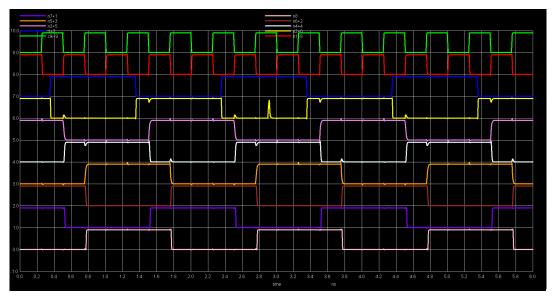

A sensibilidade do dispositivo a esse excesso de carga deve ser levada em conta, pois é definida principalmente pela capacitância do nó, pela tensão de operação alimentação do circuito) e também é dependente da capacidade dos transistores de realimentação. Todos estes itens definem a quantidade de carga crítica ( $Q_{crit}$ ) necessária para desencadear uma mudança no estado dos dados contidos no circuito. A resposta do dispositivo é dinâmica e dependente da magnitude e do tempo de existência do pulso e, portanto, a carga crítica ( $Q_{crit}$ ) não é constante, mas dependente das características do pulso de radiação e da resposta dinâmica do próprio circuito, tornando o efeito extremamente difícil de modelar ( $\overline{DODD}$ ; SEXTON,  $\overline{1995}$ ).